Communication Processor Module

MOTOROLA MPC823e REFERENCE MANUAL 16-189

SCCs

COMMUNICATION

16

PROCESSOR MODULE

receive buffer may have been received by a serial communication controller. Thus, it

is important to check more than just one RX buffer descriptor during interrupt handling.

One common practice is to process all RX buffer descriptors in the interrupt handler

until one is found with its E bit set.

4. Reset the status bit in the buffer descriptor’s control and status field that is associated

with the interrupt. These bits do not reset after each I/O operation.

5. Clear the SCCx bit in the CISR.

6. Execute the rfi instruction.

16.9.10 Controlling SCCx Timing

When the DIAG field of the GSMR_L is programmed for normal operation, the CDx and

CTSx

signals are automatically controlled by the serial communication controllers. The TCI

bit of the GSMR_L must also be programmed for normal operation.

16.9.10.1 SYNCHRONOUS PROTOCOLS. In synchronous protocols, the RTSx

pin is

asserted when SCCx data is loaded into the transmit FIFO and a falling transmit clock

occurs. At this point, the serial communication controller starts transmitting data once the

appropriate conditions occur on the CTSx

pin. In all cases, the first bit of data is the start of

the opening flag, sync pattern, or preamble.

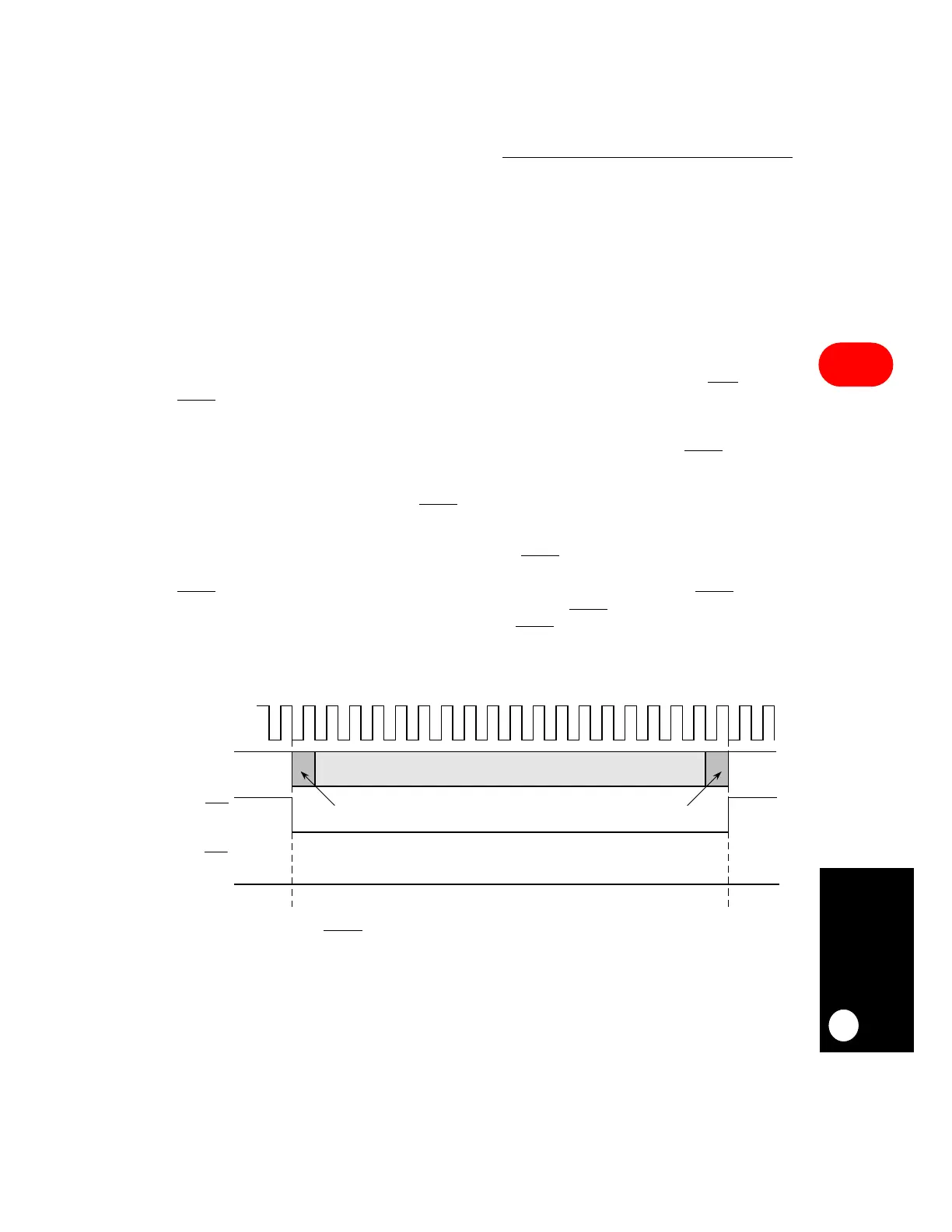

Figure 16-66 illustrates that the delay between the RTSx

pin and data is 0 bit times,

regardless of how the CTSS bit is set in the GSMR_H. This operation assumes that the

CTSx

pin is already asserted to a serial communication controller or that the CTSx pin is

reprogrammed to be a parallel I/O line, in which case, the CTSx

signal to the serial

communication controller is always asserted. The RTSx

pin is negated one clock after the

last bit in the frame.

Figure 16-66. RTSx

Output Delays Asserted for Synchronous Protocols

TXDx

RTSx

CTSx

FIRST BIT OF FRAME DATA

(INPUT)

TCLK

(OUTPUT)

(OUTPUT)

NOTE: A frame includes opening and closing flags and syncs, if present in the protocol.

LAST BIT OF FRAME DATA

Loading...

Loading...