Communication Processor Module

16-190 MPC823e REFERENCE MANUAL MOTOROLA

SCCs

COMMUNICATION

16

PROCESSOR MODULE

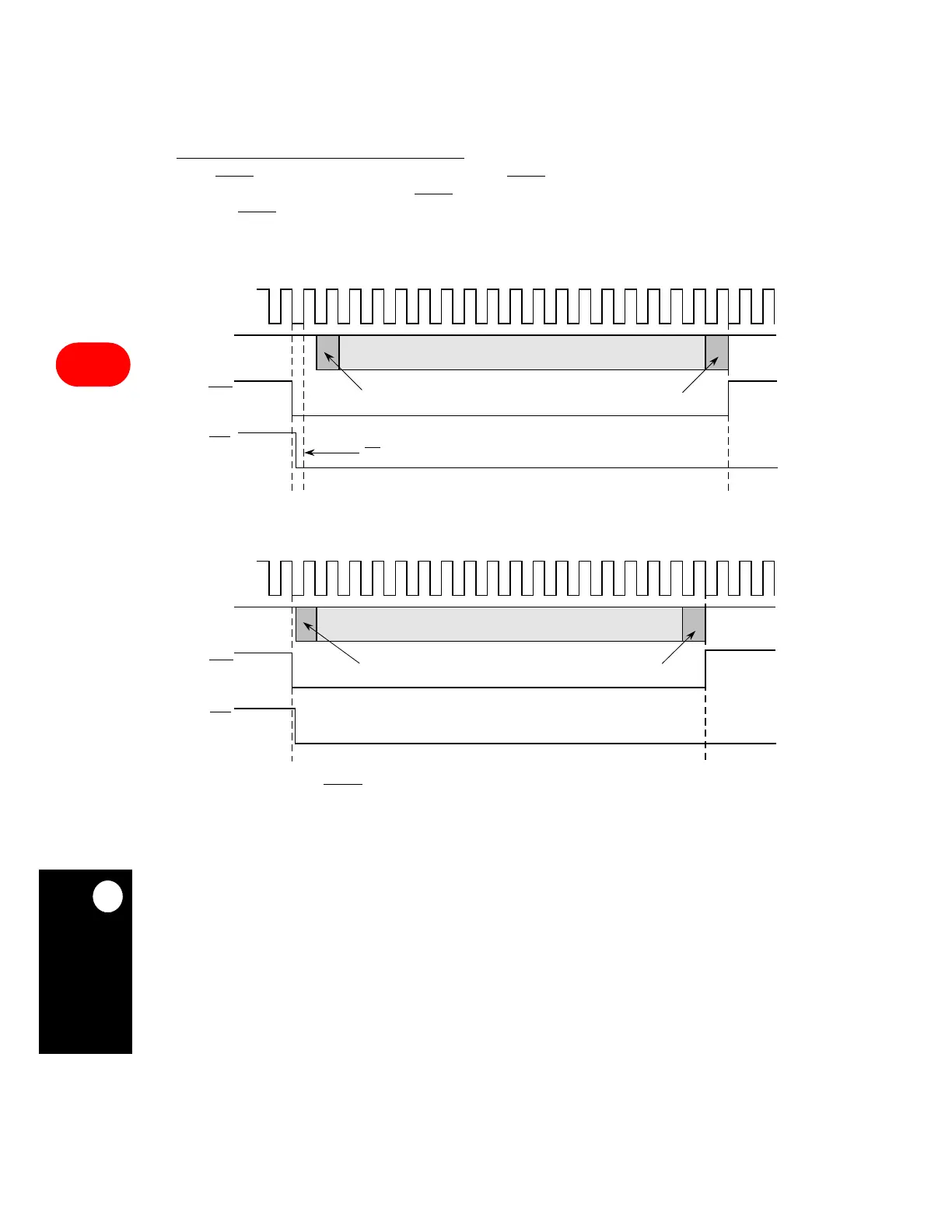

If the CTSx pin is not already asserted when the RTSx pin is asserted, then the delays to

the first bit of data depend on when CTSx

is asserted. Figure 16-67 illustrates that the delay

between CTSx

and the data can be approximately 0.5- to 1-bit time or 0-bit times, depending

on how the CTSS bit is set in the GSMR_H.

Figure 16-67. CTSx

Output Delays Asserted for Synchronous Protocols

TXDx

RTSx

CTSx

FIRST BIT OF FRAME DATA

LAST BIT OF FRAME DATA

(INPUT)

TCLK

(OUTPUT)

(OUTPUT)

NOTE: CTSS is set to 1 in the GSMR. CTSP is a "don't care".

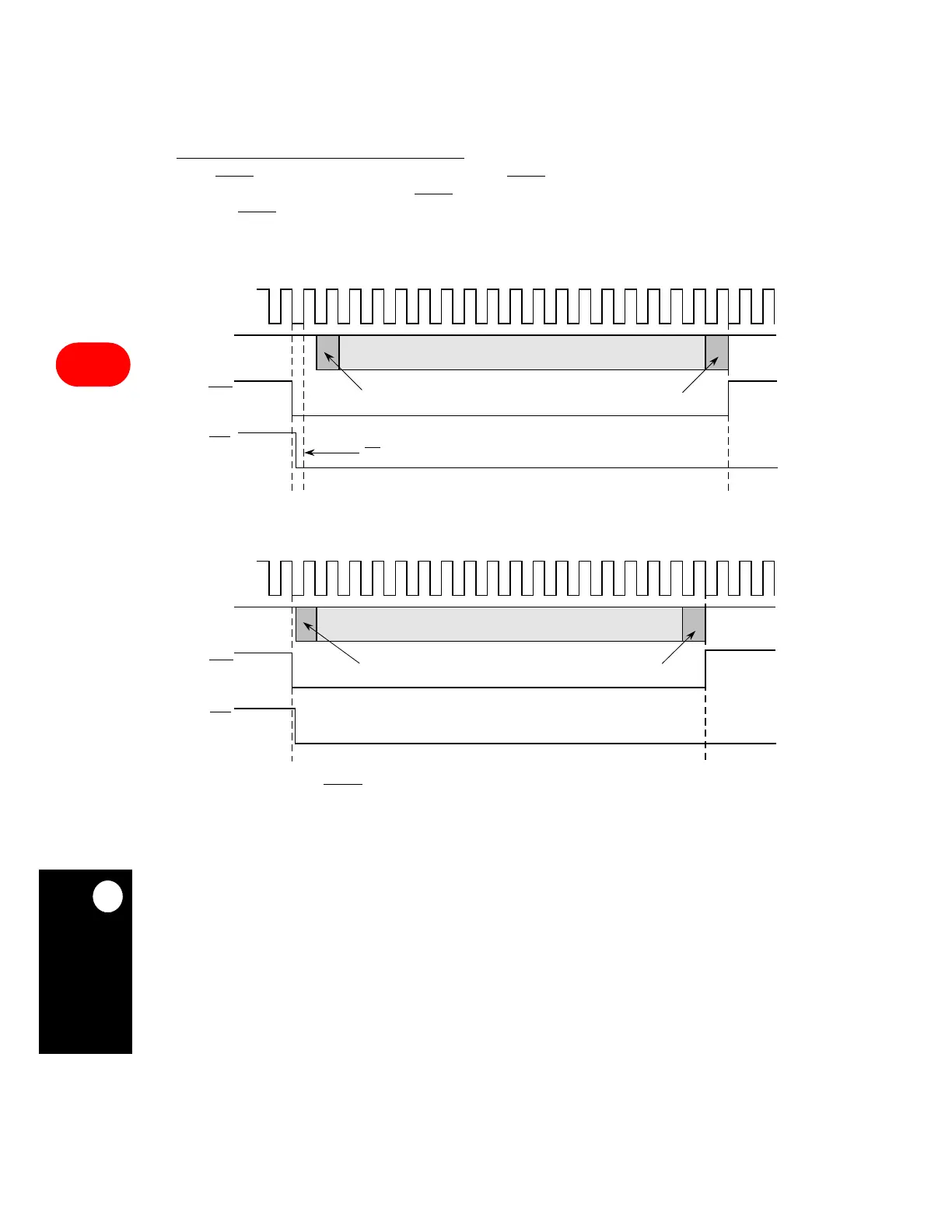

TXDx

RTSx

CTSx

FIRST BIT OF FRAME DATA

LAST BIT OF FRAME DATA

(INPUT)

TCLK

(OUTPUT)

(OUTPUT)

NOTE: CTSS is set to 0 in the GSMR. CTSP is a "don't care".

CTS SAMPLED LOW HERE

Loading...

Loading...