Communication Processor Module

16-238 MPC823e REFERENCE MANUAL MOTOROLA

COMMUNICATION

16

SCCs

• TMP—A temporary register that is only used by the communication processor module.

• TMP_MB—A temporary register that is only used by the communication processor

module.

16.9.16.5 PROGRAMMING THE SCCS IN HDLC MODE.The core configures the serial

communication controllers to operate in one of the protocols set in the MODE field of the

GSMR_L. The SCCx HDLC controller uses the same data structure as other modes and it

supports multibuffer operation and address comparisons. The reception errors are reported

through the RX buffer descriptor and the transmit errors are reported through the TX buffer

descriptor.

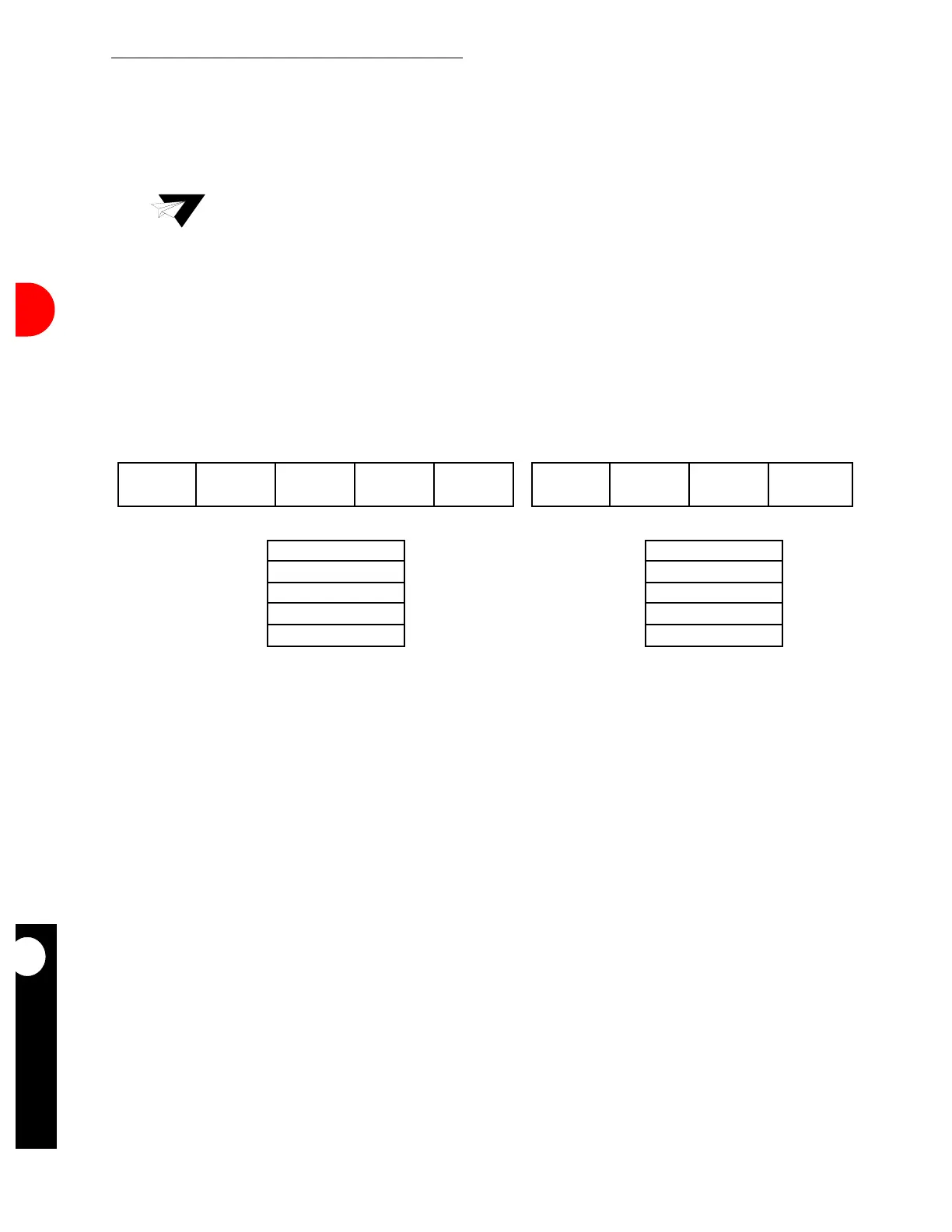

Note: For 8-bit addresses, the eight high-order bits in HMASK must be masked out

(cleared). The eight low-order bits of HMASK and HADDRx must contain the

address byte that immediately follows the opening flag. For, example, to

recognize a frame that begins 0x7E, 0x68, 0xAA, using 16-bit address

recognition, HADDRx must contain 0xAA68 and HMASK must contain 0xFFFF.

Refer to Figure 16-79 for details.

Figure 16-79. HDLC Address Recognition Example

HMASK

8-BIT ADDRESS RECOGNITION

ADDRESS

0x68

CONTROL

0x44

FLAG

0x7E

ADDRESS

0xAA

ETC.

16-BIT ADDRESS RECOGNITION

0xFFFF

0xAA68

0xFFFF

0xAA68

0xAA68

RECOGNIZES ONE 16-BIT ADDRESS (HADDR1) AND

THE 16-BIT BROADCAST ADDRESS (HADDR2)

HMASK

ADDRESS

0x55

CONTROL

0x44

FLAG

0x7E

ETC.

0x00FF

0xXX55

0xXX55

0xXX55

0xXX55

RECOGNIZES A SINGLE 8-BIT ADDRESS (HADDR1)

HADDR1

HADDR2

HADDR3

HADDR4

HADDR1

HADDR2

HADDR3

HADDR4

Loading...

Loading...