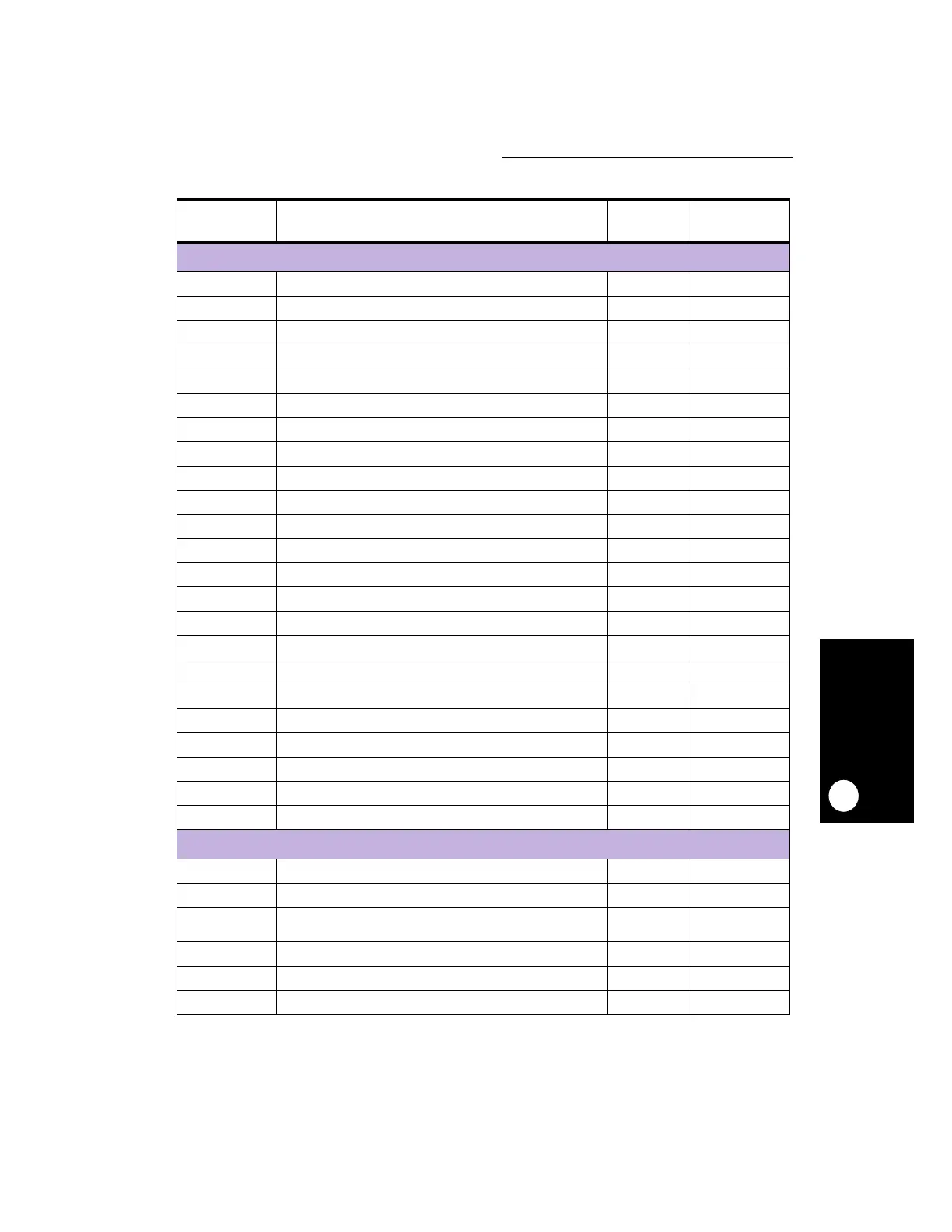

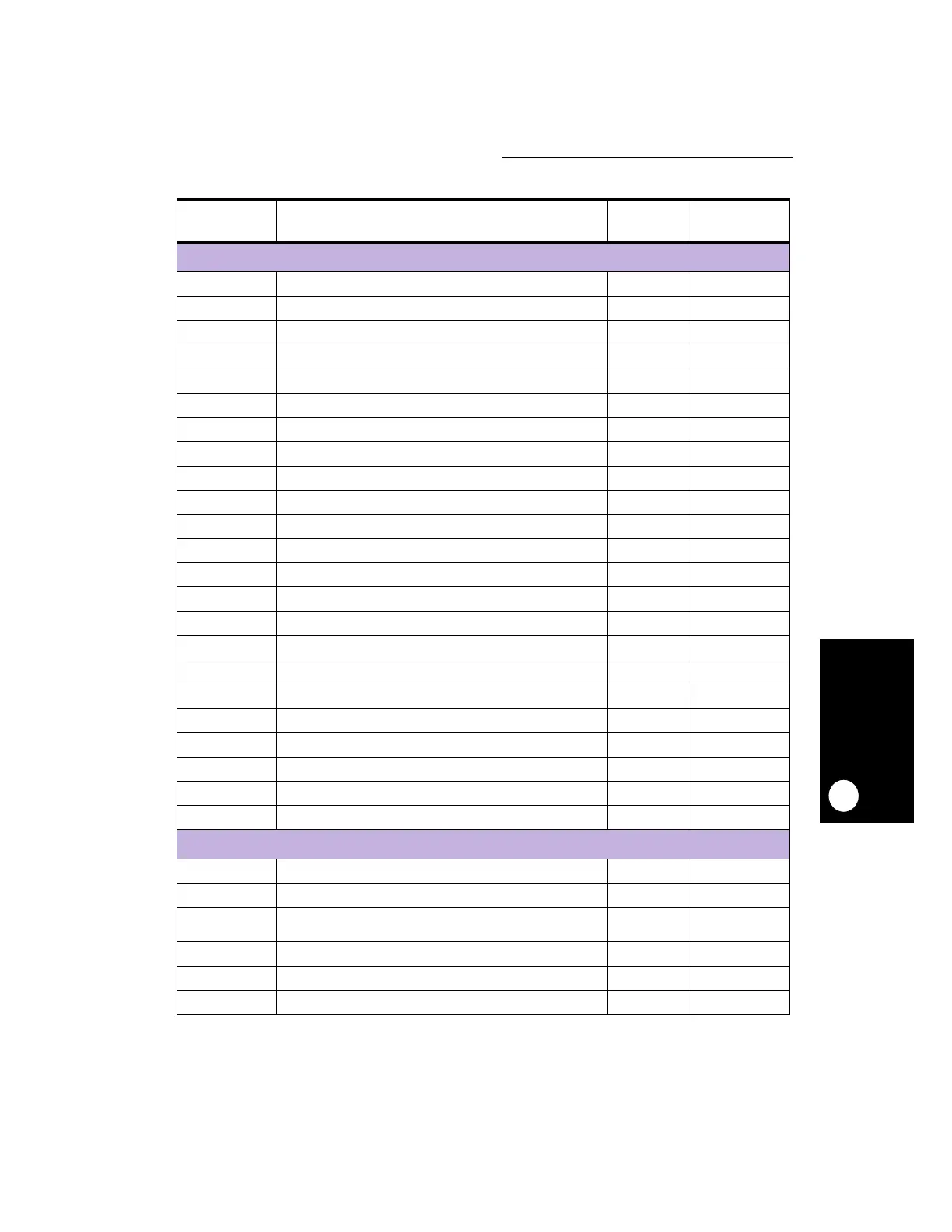

Memory Map

MOTOROLA MPC823e REFERENCE MANUAL 3-7

MEMORY MAP

3

CPM TIMERS

980 TGCR—Timer Global Configuration Register 16 16-77

982 to 98F RES—Reserved — —

990 TMR1—Timer1 Mode Register 16 16-78

992 TMR2—Timer2 Mode Register 16 16-78

994 TRR1—Timer1 Reference Register 16 16-79

996 TRR2—Timer2 Reference Register 16 16-79

998 TCR1—Timer1 Capture Register 16 16-80

99A TCR2—Timer2 Capture Register 16 16-80

99C TCN1—Timer1 Counter Register 16 16-80

99E TCN2—Timer2 Counter Register 16 16-80

9A0 TMR3—Timer3 Mode Register 16 16-78

9A2 TMR4—Timer4 Mode Register 16 16-78

9A4 TRR3—Timer3 Reference Register 16 16-79

9A6 TRR4—Timer4 Reference Register 16 16-79

9A8 TCR3—Timer3 Capture Register 16 16-80

9AA TCR4—Timer4 Capture Register 16 16-80

9AC TCN3—Timer3 Counter Register 16 16-80

9AE TCN4—Timer4 Counter Register 16 16-80

9B0 TER1—Timer1 Event Register 16 16-81

9B2 TER2—Timer2 Event Register 16 16-81

9B4 TER3—Timer3 Event Register 16 16-81

9B6 TER4—Timer4 Event Register 16 16-81

9B8 to 9BF RES—Reserved — —

COMMUNICATION PROCESSOR MODULE

9C0 CPCR—Communication Processor Module Command Register 16 16-9

9C2 to 9C3 RES—Reserved 16 —

9C4 to 9C7 RCCR/RMDS—RISC Controller Configuration Register and

RISC Microcode Development Support Control Register

32 16-7

9C8 to 9CB RES—Reserved 32 —

9CC RCTR1—RISC Controller Trap Register 1 16 —

9CE RCTR2—RISC Controller Trap Register 2 16 —

Table 3-1. MPC823e Internal Memory Map (Continued)

INTERNAL

ADDRESS REGISTER

SIZE

(IN BITS)

PAGE NUMBER

LOCATION

Loading...

Loading...