Communication Processor Module

16-432 MPC823e REFERENCE MANUAL MOTOROLA

SPI

COMMUNICATION

16

PROCESSOR MODULE

TEN—SMCx Transmit Enable

0 = SMCx transmitter disabled.

1 = SMCx transmitter enabled.

REN—SMCx Receive Enable

0 = SMCx receiver disabled.

1 = SMCx receiver enabled.

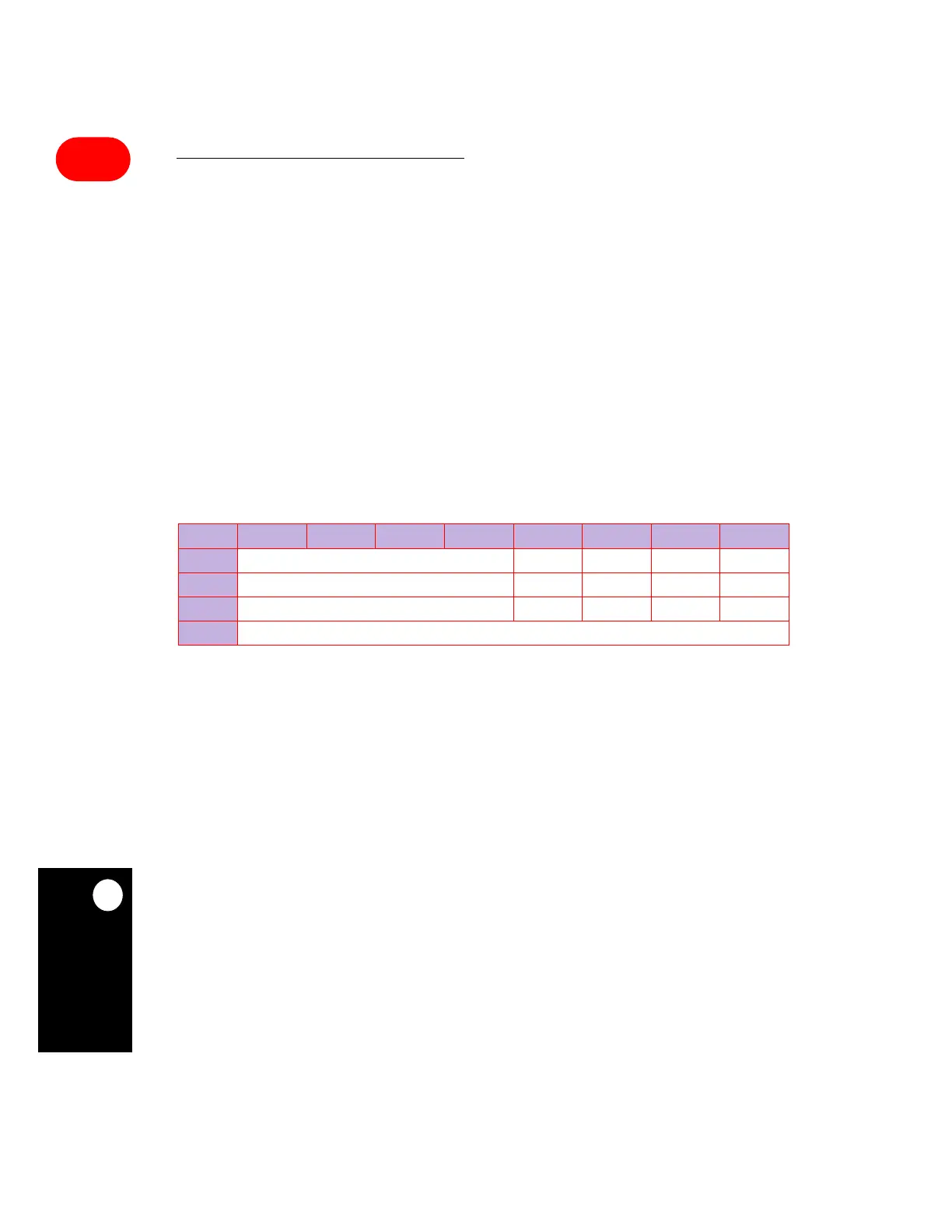

16.11.8.5 SMCx GCI EVENT REGISTER. When a serial management controller is in GCI

mode, the 8-bit memory-mapped SMCx event register is referred to as the SMCx GCI event

(SMCE–GCI) register. It is used to generate interrupts and report events recognized by the

SMCx channel. When an event is recognized, a serial management controller sets the

corresponding bit in this register. Interrupts generated by this register can be masked in the

SMCM–GCI register. A bit is cleared by writing a 1 (writing a zero has no effect) more than

one bit can be cleared at a time. All unmasked bits must be cleared before the

communication processor module clears the internal interrupt request to the CPM interrupt

controller. This register is cleared by reset and can be read at any time.

Bits 0–3—Reserved

These bits are reserved and must be set to 0.

CTXB—Circuit Interface Channel Buffer Transmitted

This bit indicates that the circuit interface transmit buffer is now empty.

CRXB—Circuit Interface Channel Buffer Received

This bit indicates when the circuit interface receive buffer is full.

MTXB—Monitor Channel Buffer Transmitted

This bit indicates that the monitor transmit buffer is now empty.

MRXB—Monitor Channel Buffer Received

This bit indicates when the monitor receive buffer is full.

SMCE–GCI

BIT 0 1 2 3 4 5 6 7

FIELD RESERVED CTXB CRXB MTXB MRXB

RESET 0 0000

R/W R/W R/W R/W R/W R/W

ADDR (IMMR & 0xFFFF0000) + 0xA86 (SMC1), 0xA96 (SMC2)

Loading...

Loading...