PCMCIA Interface

MOTOROLA

MPC823e REFERENCE MANUAL

17-13

PCMCIA INTERFACE

17

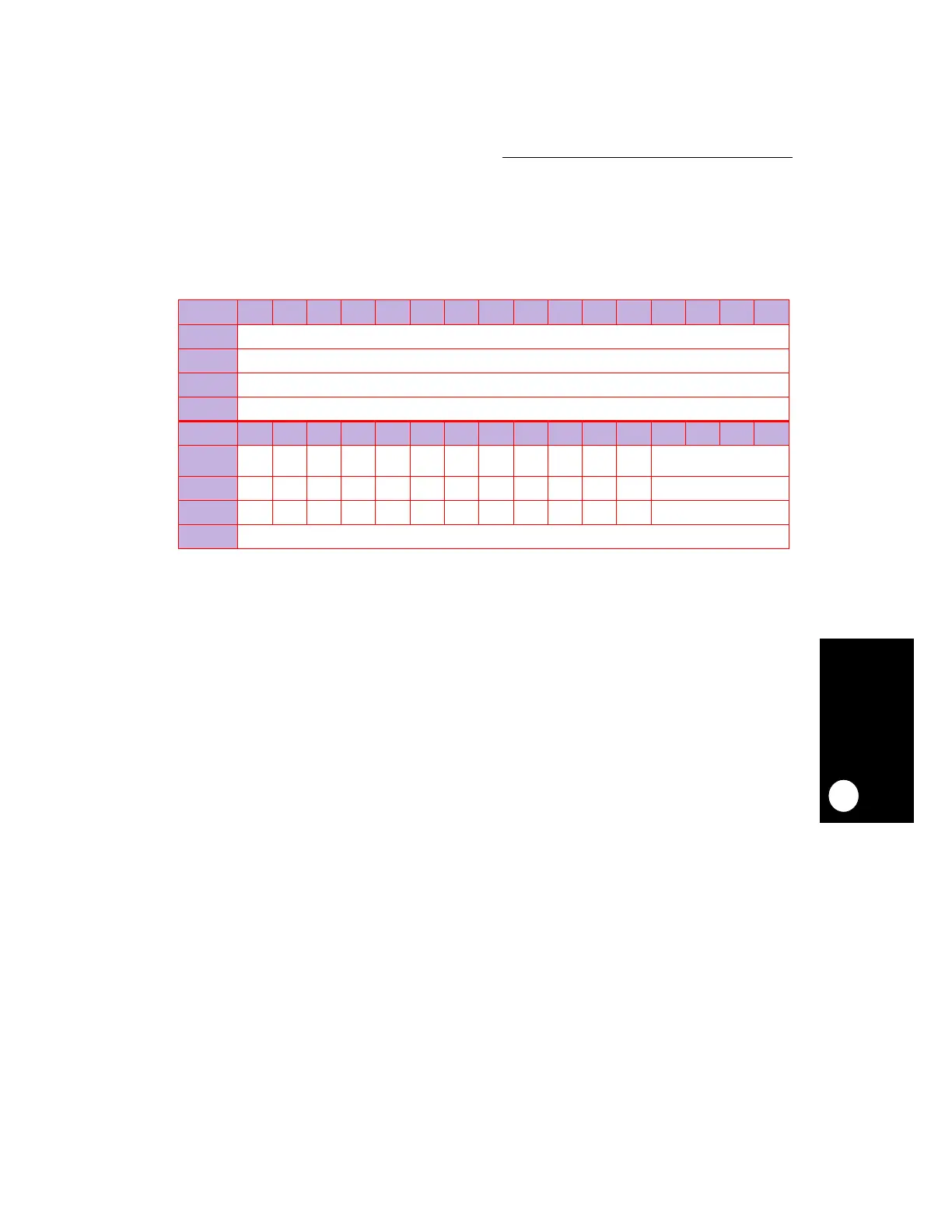

17.5.3 PCMCIA Interface Enable Register

The PCMCIA interface enable register (PER) acts as a mask for the various sources of a

PCMCIA interrupt. Interrupts caused by bits 16-22 are reported as CBSCHLVL interrupts,

while interrupts caused by bits 24-27 are reported as CBIRQLVL interrupts.

Bits 0–15—Reserved

These bits are reserved and must be set to 0.

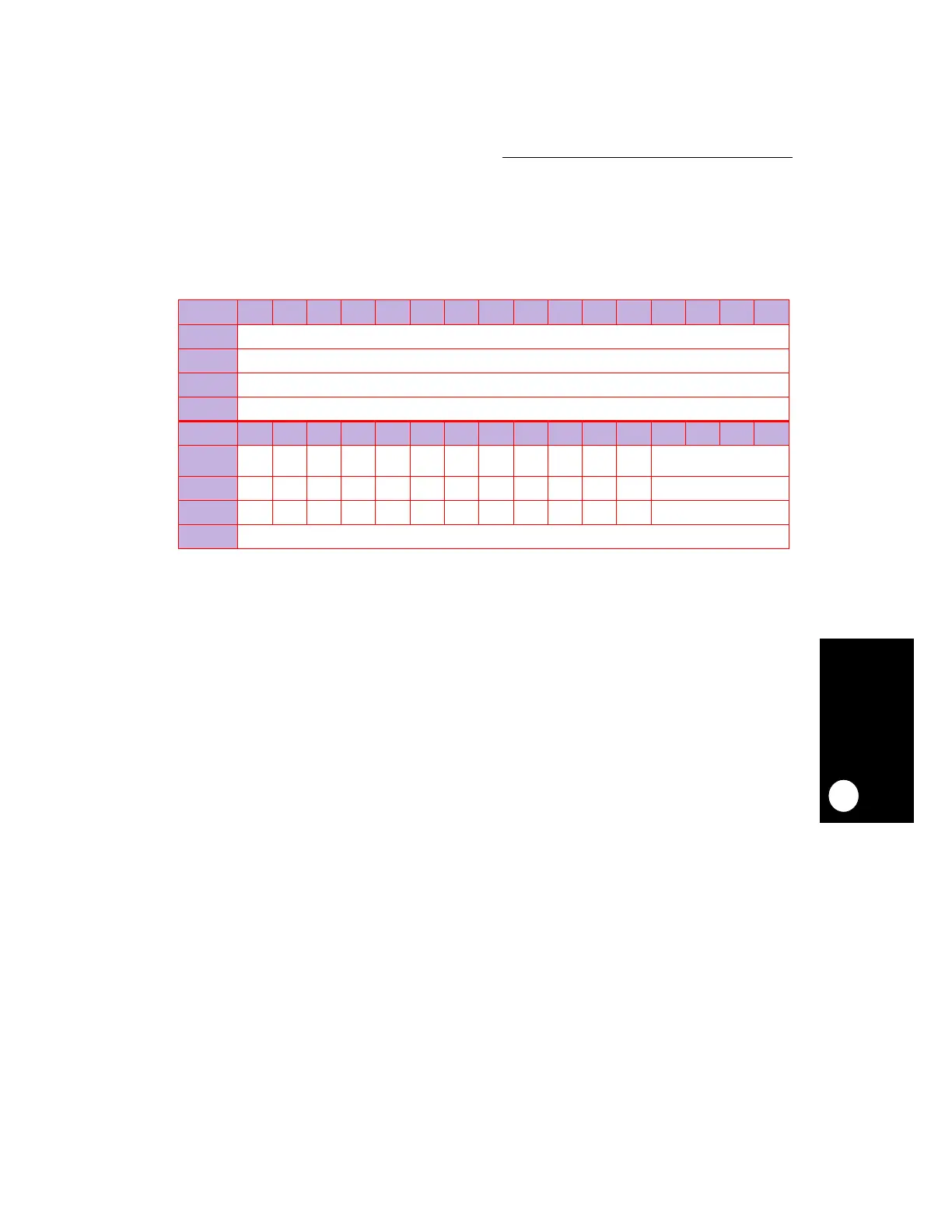

CB_EVS1—Card B Enable for Voltage Sense 1

0 = Disable interrupt on any change in the relevant pin.

1 = Enable interrupt on changes in the relevant pin.

CB_EVS2—Card B Enable for Voltage Sense 2

0 = Disable interrupt on any change in the relevant pin.

1 = Enable interrupt on changes in the relevant pin.

CB_EWP—Card B Enable for Write-Protect

0 = Disable interrupt on any change in the relevant pin.

1 = Enable interrupt on changes in the relevant pin.

CB_ECD2—Card B Enable for Card Detect 2

0 = Disable interrupt on any change in the relevant pin.

1 = Enable interrupt on changes in the relevant pin.

CB_ECD1—Card B Enable for Card Detect 1

0 = Disable interrupt on any change in the relevant pin.

1 = Enable interrupt on changes in the relevant pin.

PER

BIT

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

FIELD

RESERVED

RESET

—

R/W

R/W

ADDR

(IMMR & 0xFFFF0000) + 0xF8

BIT

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

FIELD

CB_EV

S1

CB_EV

S2

CB_EW

P

CB_EC

D2

CB_EC

D1

CB_EB

VD2

CB_EB

VD1

RES

CB_ER

DY_L

CB_ER

DY_H

CB_ER

DY_R

CB_ER

DY_F

RESERVED

RESET

———————————— —

R/W

R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W

ADDR

(IMMR & 0xFFFF0000) + 0xF8

NOTE: — = Undefined.

Loading...

Loading...