© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

User manual Rev. 01 — 12 January 2006 163

Philips Semiconductors

UM10161

Volume 1 Chapter 12: SPI

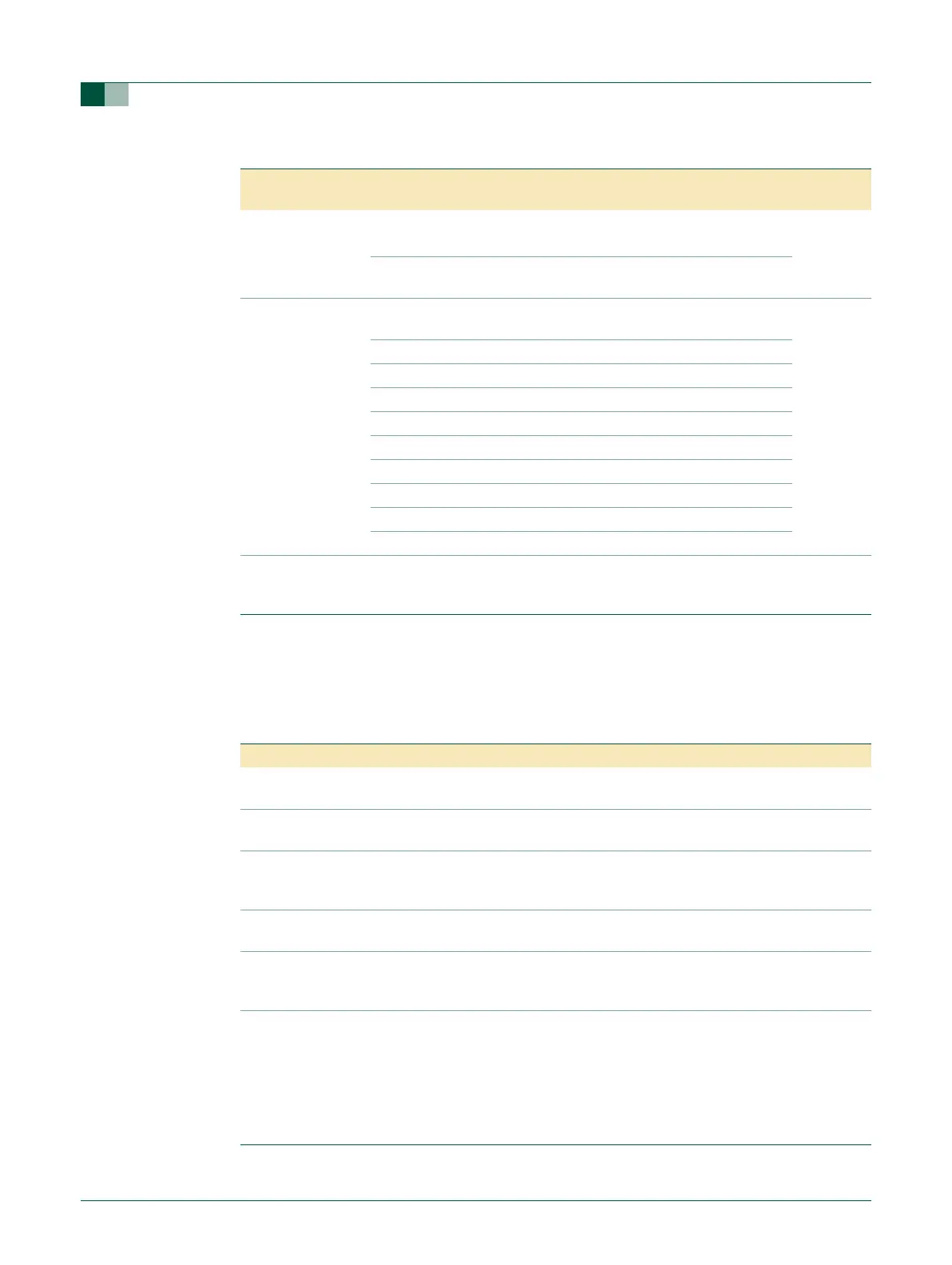

12.4.2 SPI Status Register (S0SPSR - 0xE002 0004)

The S0SPSR register controls the operation of the SPI0 as per the configuration bits

setting.

7 SPIE

0

Serial peripheral interrupt enable.

SPI interrupts are inhibited.

0

1 A hardware interrupt is generated each time the SPIF or

MODF bits are activated.

11:8 BITS When bit 2 of this register is 1, this field controls the

number of bits per transfer:

0000

1000 8 bits per transfer

1001 9 bits per transfer

1010 10 bits per transfer

1011 11 bits per transfer

1100 12 bits per transfer

1101 13 bits per transfer

1110 14 bits per transfer

1111 15 bits per transfer

0000 16 bits per transfer

15:12 - Reserved, user software should not write ones to

reserved bits. The value read from a reserved bit is not

defined.

NA

Table 141: SPI Control Register (S0SPCR - address 0xE002 0000) bit description

Bit Symbol Value Description Reset

value

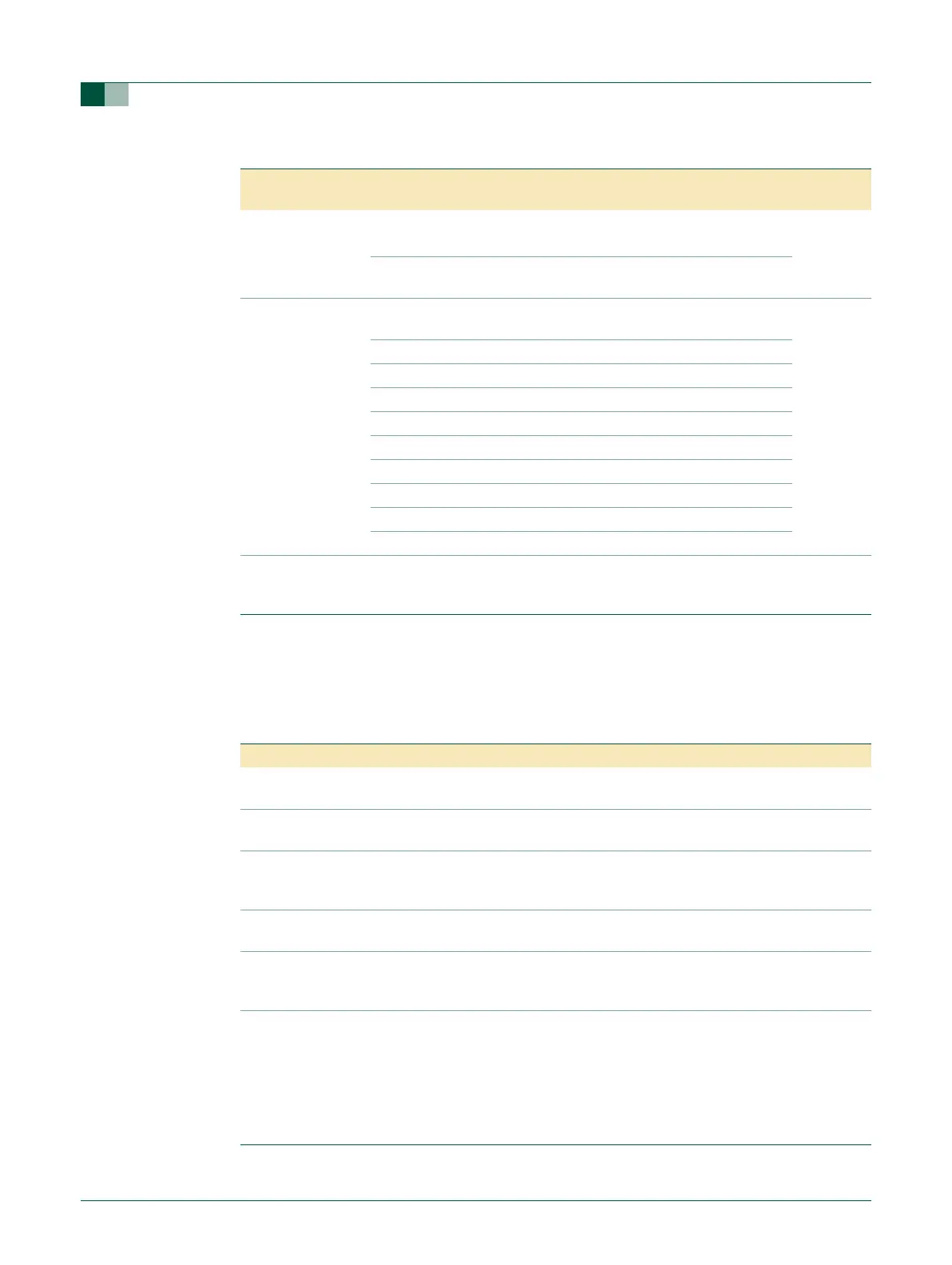

Table 142: SPI Status Register (S0SPSR - address 0xE002 0004) bit description

Bit Symbol Description Reset value

2:0 - Reserved, user software should not write ones to reserved bits.

The value read from a reserved bit is not defined.

NA

3 ABRT Slave abort. When 1, this bit indicates that a slave abort has

occurred. This bit is cleared by reading this register.

0

4 MODF Mode fault. when 1, this bit indicates that a Mode fault error has

occurred. This bit is cleared by reading this register, then writing

the SPI0 control register.

0

5 ROVR Read overrun. When 1, this bit indicates that a read overrun has

occurred. This bit is cleared by reading this register.

0

6 WCOL Write collision. When 1, this bit indicates that a write collision

has occurred. This bit is cleared by reading this register, then

accessing the SPI data register.

0

7 SPIF SPI transfer complete flag. When 1, this bit indicates when a SPI

data transfer is complete. When a master, this bit is set at the

end of the last cycle of the transfer. When a slave, this bit is set

on the last data sampling edge of the SCK. This bit is cleared by

first reading this register, then accessing the SPI data register.

Note: this is not the SPI interrupt flag. This flag is found in the

SPINT register.

0

Loading...

Loading...