© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

User manual Rev. 01 — 12 January 2006 88

Philips Semiconductors

UM10161

Volume 1 Chapter 9: UART0

9.3.7 UART0 Interrupt Identification Register (U0IIR - 0xE000 C008, Read

Only)

The U0IIR provides a status code that denotes the priority and source of a pending

interrupt. The interrupts are frozen during an U0IIR access. If an interrupt occurs during

an U0IIR access, the interrupt is recorded for the next U0IIR access.

Interrupts are handled as described in Tabl e 90

. Given the status of U0IIR[3:0], an

interrupt handler routine can determine the cause of the interrupt and how to clear the

active interrupt. The U0IIR must be read in order to clear the interrupt prior to exiting the

Interrupt Service Routine.

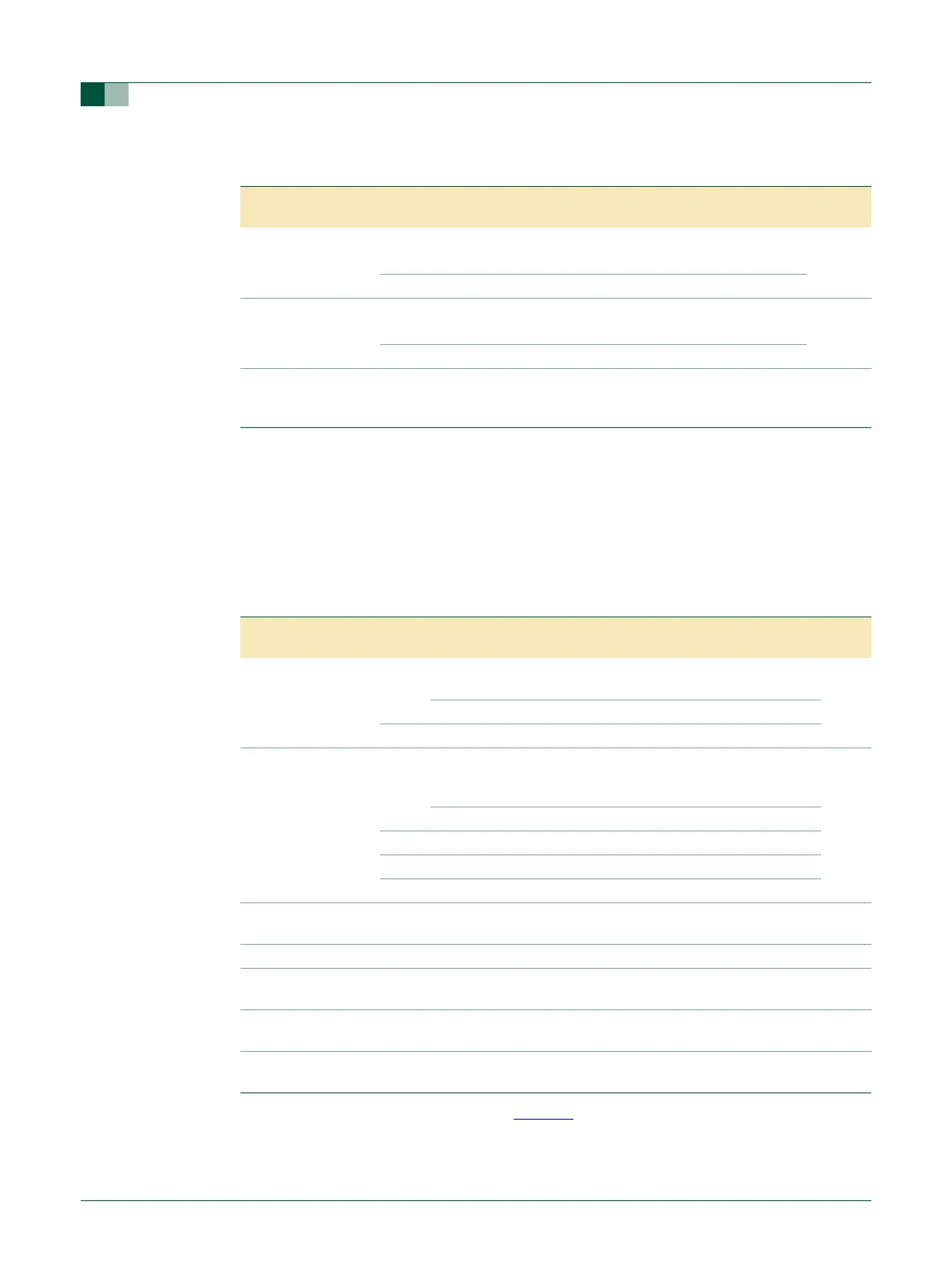

8 ABTOIntEn

0

U0IER8 enables the auto-baud time-out interrupt.

Disable Auto-baud Time-out Interrupt.

0

1 Enable Auto-baud Time-out Interrupt.

9 ABEOIntEn

0

U0IER9 enables the end of auto-baud interrupt.

Disable End of Auto-baud Interrupt.

0

1 Enable End of Auto-baud Interrupt.

31:10 - - Reserved, user software should not write ones to

reserved bits. The value read from a reserved bit is not

defined.

NA

Table 88: UART0 Interrupt Enable Register (U0IER - address 0xE000 C004, when DLAB = 0)

bit description

Bit Symbol Value Description Reset

value

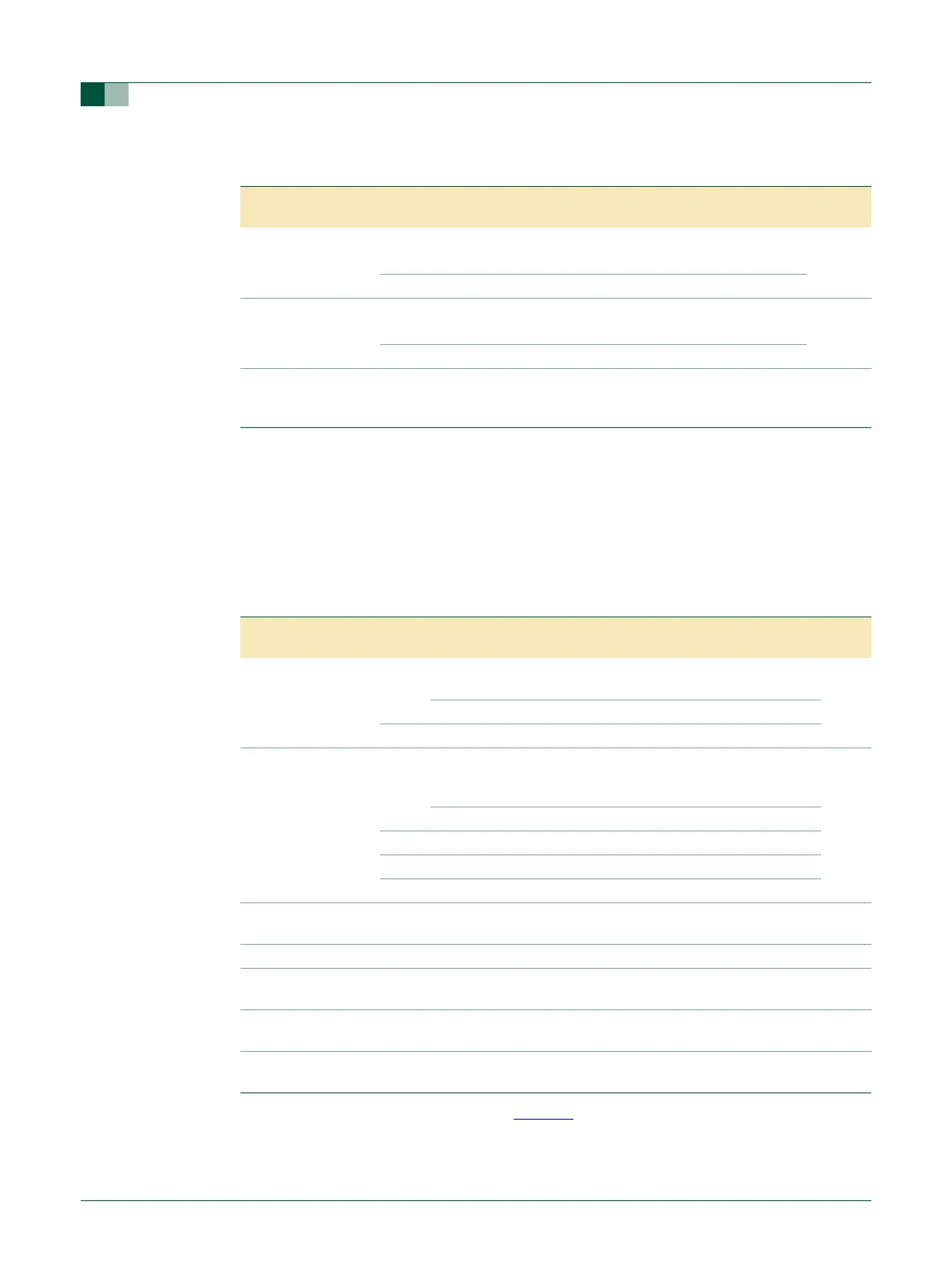

Table 89: UART0 Interrupt Identification Register (UOIIR - address 0xE000 C008, read only)

bit description

Bit Symbol Value Description Reset

value

0 Interrupt

Pending

0

Note that U0IIR[0] is active LOW. The pending interrupt can

be determined by evaluating U0IIR[3:1].

1

At least one interrupt is pending.

1 No pending interrupts.

3:1 Interrupt

Identification

011

U0IER[3:1] identifies an interrupt corresponding to the

UART0 Rx FIFO. All other combinations of U0IER[3:1] not

listed above are reserved (000,100,101,111).

0

1 - Receive Line Status (RLS).

010 2a - Receive Data Available (RDA).

110 2b - Character Time-out Indicator (CTI).

001 3 - THRE Interrupt

5:4 - Reserved, user software should not write ones to reserved

bits. The value read from a reserved bit is not defined.

NA

7:6 FIFO Enable These bits are equivalent to U0FCR[0]. 0

8 ABEOInt End of auto-baud interrupt. True if auto-baud has finished

successfully and interrupt is enabled.

0

9 ABTOInt Auto-baud time-out interrupt. True if auto-baud has timed

out and interrupt is enabled.

0

31:10 - Reserved, user software should not write ones to reserved

bits. The value read from a reserved bit is not defined.

NA

Loading...

Loading...