© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

User manual Rev. 01 — 12 January 2006 64

Philips Semiconductors

UM10161

Volume 1 Chapter 6: Pin configuration

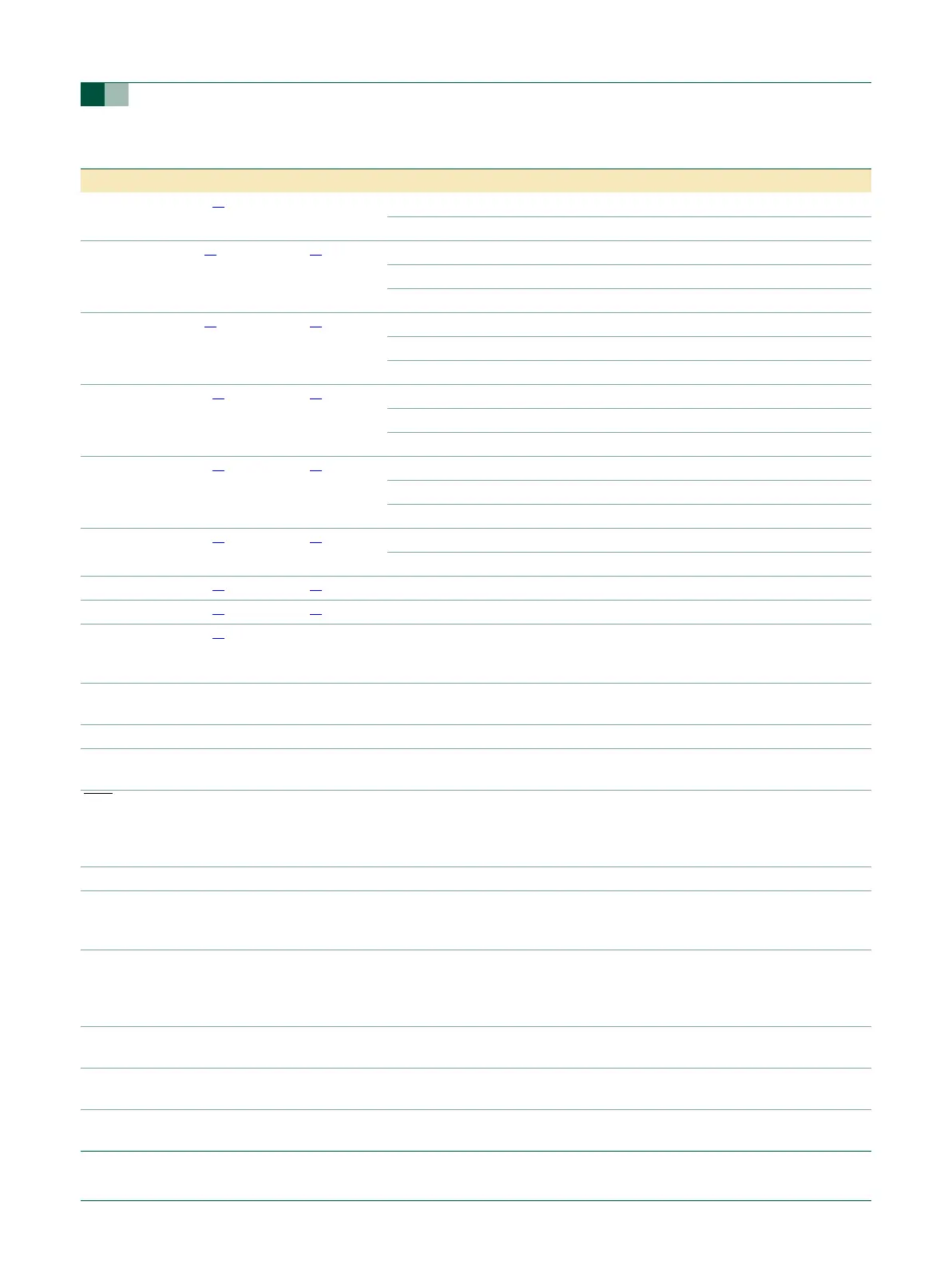

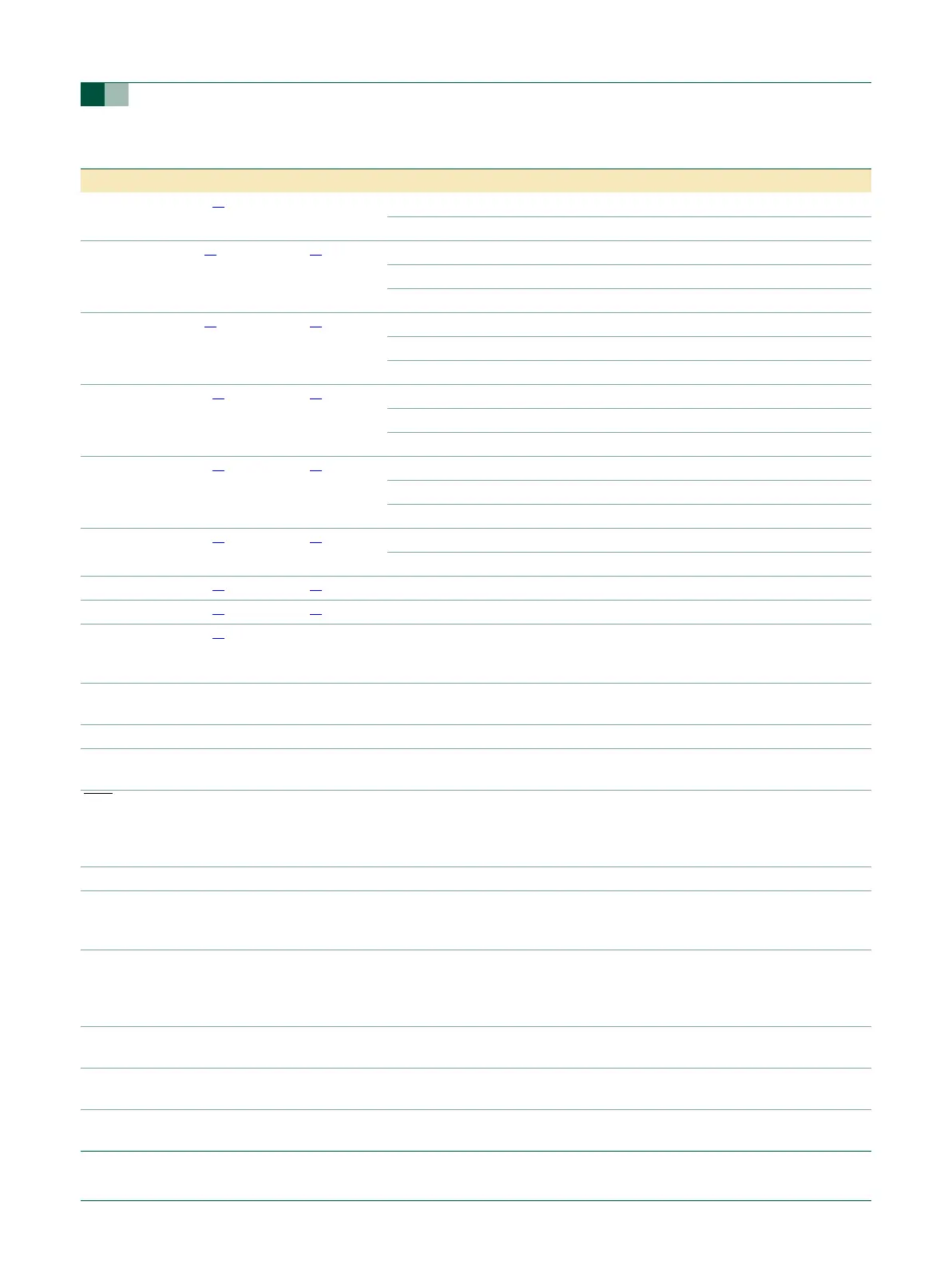

[1] 5 V tolerant pad providing digital I/O functions with TTL levels and hysteresis and 10 ns slew rate control.

P0.26/AD0.7 39

[1]

n.c. I/O P0.26 — General purpose Input/output digital pin (GPIO).

I AD0.7 — Analog Input 7.

P0.27/TRST/

CAP2.0

8

[4]

13

[4]

I/O P0.27 — General purpose Input/output digital pin (GPIO).

I TRST — Test Reset for JTAG interface.

I CAP2.0 — Capture input for Timer 2, channel 0.

P0.28/TMS/

CAP2.1

9

[4]

14

[4]

I/O P0.28 — General purpose Input/output digital pin (GPIO).

I TMS — Test Mode Select for JTAG interface.

I CAP2.1 — Capture input for Timer 2, channel 1.

P0.29/TCK/

CAP2.2

10

[4]

15

[4]

I/O P0.29 — General purpose Input/output digital pin (GPIO).

I TCK — Test Clock for JTAG interface.

I CAP2.2 — Capture input for Timer 2, channel 2.

P0.30/TDI/

MAT3.3

15

[4]

20

[4]

I/O P0.30 — General purpose Input/output digital pin (GPIO).

I TDI — Test Data In for JTAG interface.

O MAT3.3 — PWM output 3 for Timer 3.

P0.31/TDO 16

[4]

21

[4]

O P0.31 — General purpose output only digital pin (GPIO).

O TDO — Test Data Out for JTAG interface.

RTXC1 20

[5]

24

[5]

I Input to the RTC oscillator circuit.

RTXC2 25

[5]

29

[5]

O Output from the RTC oscillator circuit.

RTCK 26

[5]

n.c. I/O Returned test clock output: Extra signal added to the JTAG

port. Assists debugger synchronization when processor

frequency varies. Bidirectional pin with internal pull-up.

X1 11 16 I Input to the oscillator circuit and internal clock generator

circuits.

X2 12 17 O Output from the oscillator amplifier.

DBGSEL 27 30 I Debug select: When LOW, the part operates normally. When

HIGH, debug mode is entered. Input with internal pull-down.

RST

611IExternal reset input: A LOW on this pin resets the device,

causing I/O ports and peripherals to take on their default

states and processor execution to begin at address 0. TTL

with hysteresis, 5 V tolerant.

V

SS

7, 19, 43 1, 12, 23 I Ground: 0 V reference.

V

SSA

31 34 I Analog ground: 0 V reference. This should be nominally the

same voltage as V

SS

but should be isolated to minimize noise

and error.

V

DDA

42 44 I Analog 3.3 V power supply: This should be nominally the

same voltage as V

DD(3V3)

but should be isolated to minimize

noise and error. This voltage is used to power the on-chip

PLL.

V

DD(1V8)

510I1.8 V core power supply: This is the power supply voltage for

internal circuitry.

V

DD(3V3)

17, 40 42 I 3.3 V pad power supply: This is the power supply voltage for

the I/O ports.

VBAT 4 n.c. I RTC power supply: 3.3 V on this pin supplies the power to

the RTC.

Table 58: Pin description

…continued

Symbol LQFP48 PLCC44 Type Description

Loading...

Loading...