© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

User manual Rev. 01 — 12 January 2006 47

Philips Semiconductors

UM10161

Volume 1 Chapter 5: VIC

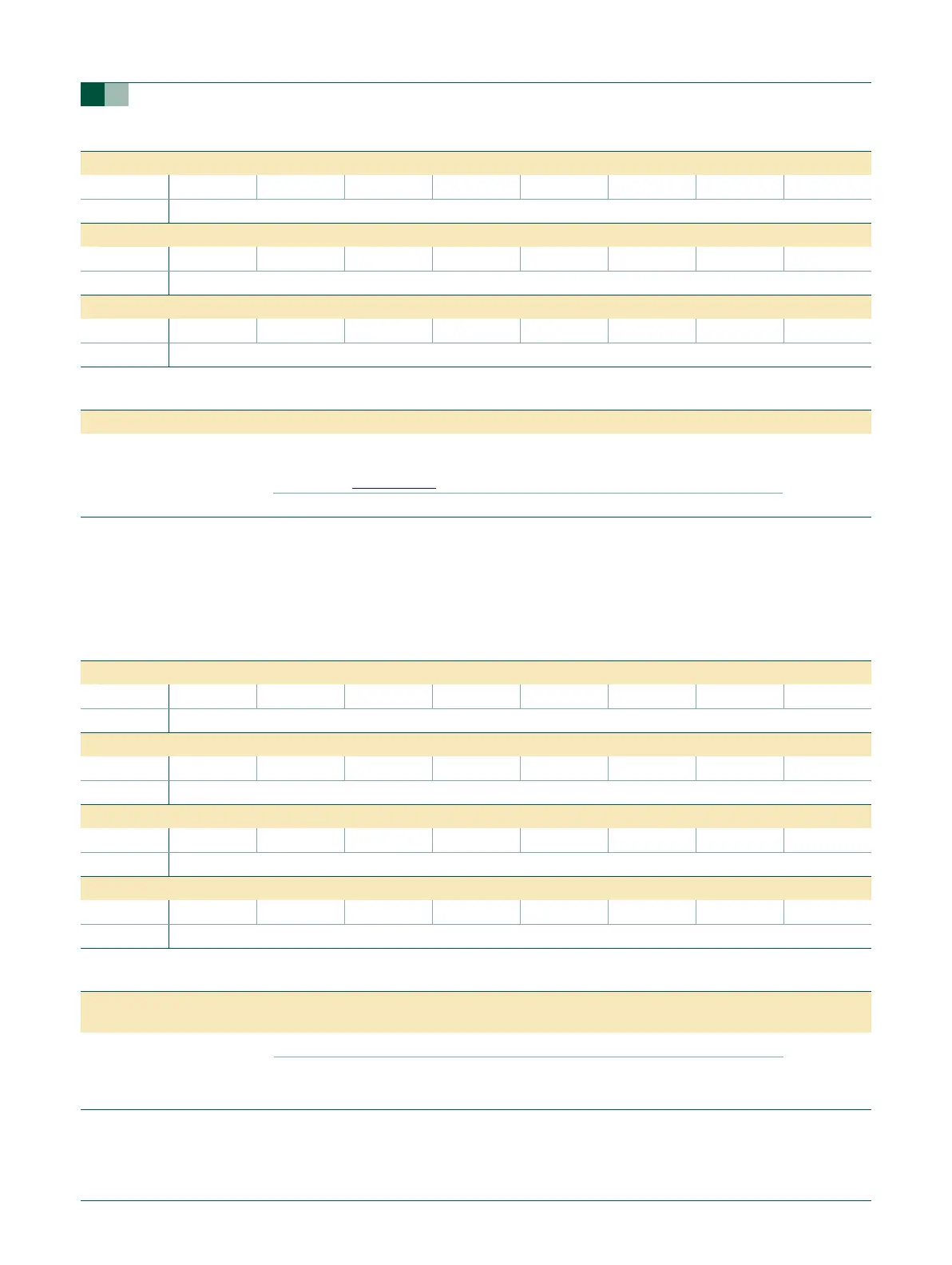

5.4.2 Software Interrupt Clear register (VICSoftIntClear - 0xFFFF F01C)

This register allows software to clear one or more bits in the Software Interrupt register,

without having to first read it.

Bit 23 22 21 20 19 18 17 16

Symbol ----I2C1AD0-EINT2

Access R/W R/W R/W R/W R/W R/W R/W R/W

Bit 15 14 13 12 11 10 9 8

Symbol EINT1 EINT0 RTC PLL SSP/SPI1 SPI0 I2C0 -

Access R/W R/W R/W R/W R/W R/W R/W R/W

Bit 7 6 5 4 3 2 1 0

Symbol UART1 UART0 TIMER1 TIMER0 ARMCore1 ARMCore0 - WDT

Access R/W R/W R/W R/W R/W R/W R/W R/W

Table 37: Software Interrupt register (VICSoftInt - address 0xFFFF F018) bit description

Bit Symbol Value Description Reset value

31:0 See VICSoftInt

bit allocation

table.

0 Do not force the interrupt request with this bit number. Writing

zeroes to bits in VICSoftInt has no effect, see VICSoftIntClear

(Section 5.4.2

).

0

1 Force the interrupt request with this bit number.

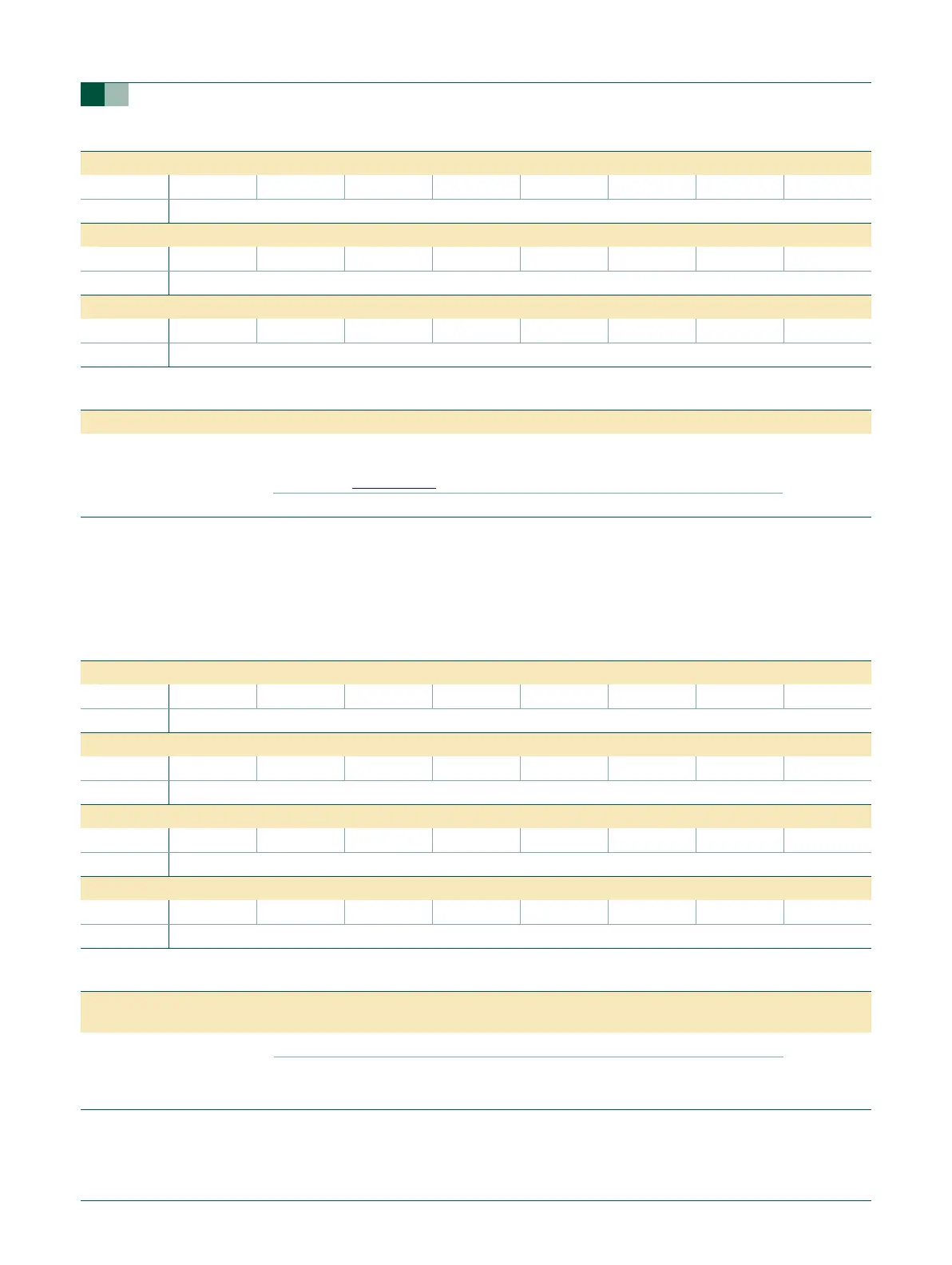

Table 38: Software Interrupt Clear register (VICSoftIntClear - address 0xFFFF F01C) bit allocation

Reset value: 0x0000 0000

Bit 31 30 29 28 27 26 25 24

Symbol ----TIMER3TIMER2--

Access WO WO WO WO WO WO WO WO

Bit 23 22 21 20 19 18 17 16

Symbol ----I2C1AD0-EINT2

Access WO WO WO WO WO WO WO WO

Bit 15 14 13 12 11 10 9 8

Symbol EINT1 EINT0 RTC PLL SSP/SPI1 SPI0 I2C0 -

Access WO WO WO WO WO WO WO WO

Bit 7 6 5 4 3 2 1 0

Symbol UART1 UART0 TIMER1 TIMER0 ARMCore1 ARMCore0 - WDT

Access WO WO WO WO WO WO WO WO

Table 39: Software Interrupt Clear register (VICSoftIntClear - address 0xFFFF F01C) bit description

Bit Symbol Value Description Reset

value

31:0 See

VICSoftIntClea

r bit allocation

table.

0 Writing a 0 leaves the corresponding bit in VICSoftInt unchanged. 0

1 Writing a 1 clears the corresponding bit in the Software Interrupt

register, thus releasing the forcing of this request.

Loading...

Loading...