© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

User manual Rev. 01 — 12 January 2006 175

Philips Semiconductors

UM10161

Volume 1 Chapter 13: SSP

[1] Reset value reflects the data stored in used bits only. It does not include reserved bits content.

13.4.1 SSP Control Register 0 (SSPCR0 - 0xE006 8000)

This register controls the basic operation of the SSP controller.

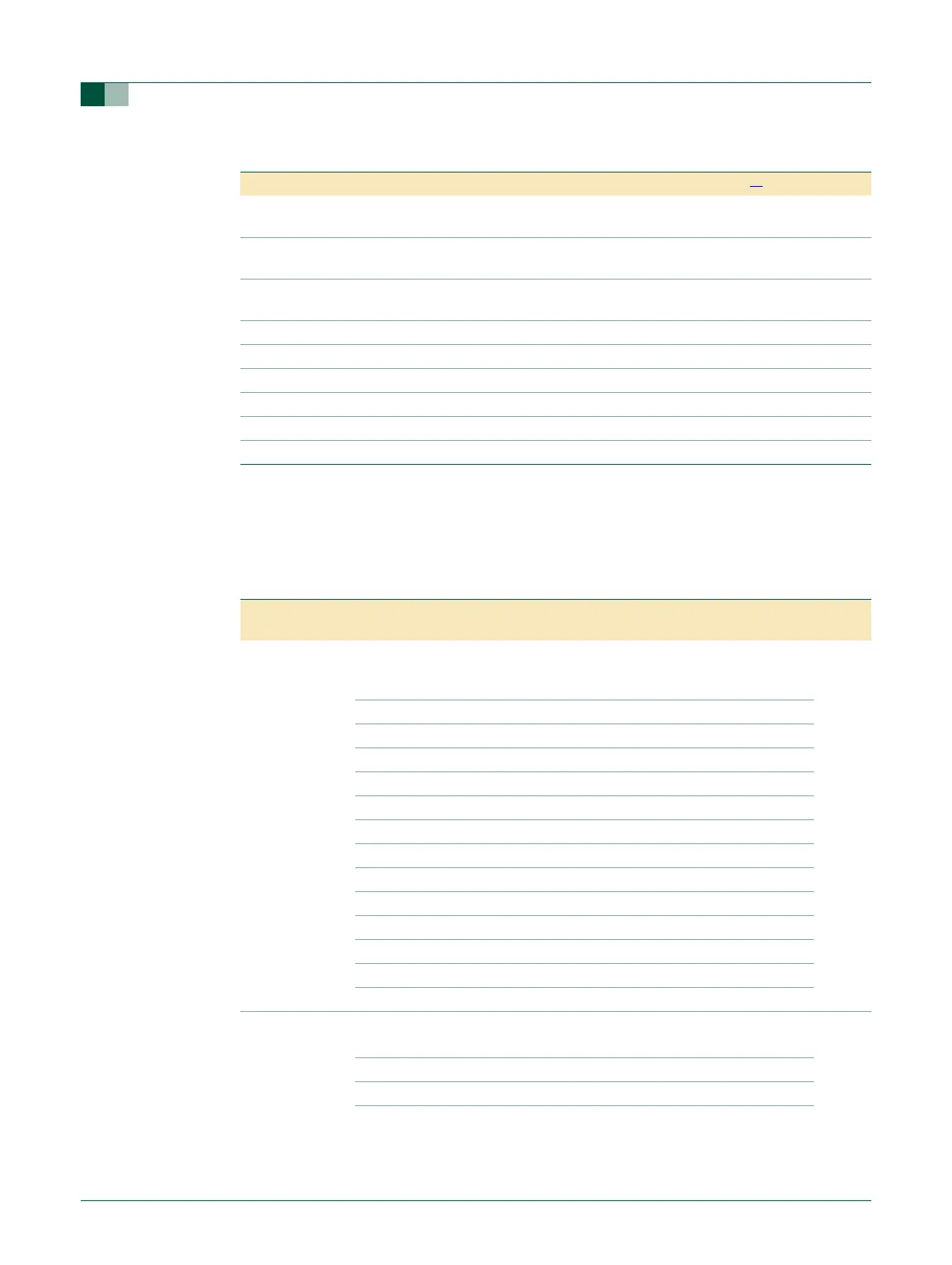

Table 147: SSP register map

Name Description Access Reset value

[1]

Address

SSPCR0 Control Register 0. Selects the serial clock

rate, bus type, and data size.

R/W 0x0000 0xE006 8000

SSPCR1 Control Register 1. Selects master/slave

and other modes.

R/W 0x00 0xE006 8004

SSPDR Data Register. Writes fill the transmit FIFO,

and reads empty the receive FIFO.

R/W 0x0000 0xE006 8008

SSPSR Status Register RO 0x03 0xE006 800C

SSPCPSR Clock Prescale Register R/W 0x00 0xE006 8010

SSPIMSC Interrupt Mask Set and Clear Register R/W 0x00 0xE006 8014

SSPRIS Raw Interrupt Status Register R/W 0x04 0xE006 8018

SSPMIS Masked Interrupt Status Register RO 0x00 0xE006 801C

SSPICR SSPICR Interrupt Clear Register WO NA 0xE006 8020

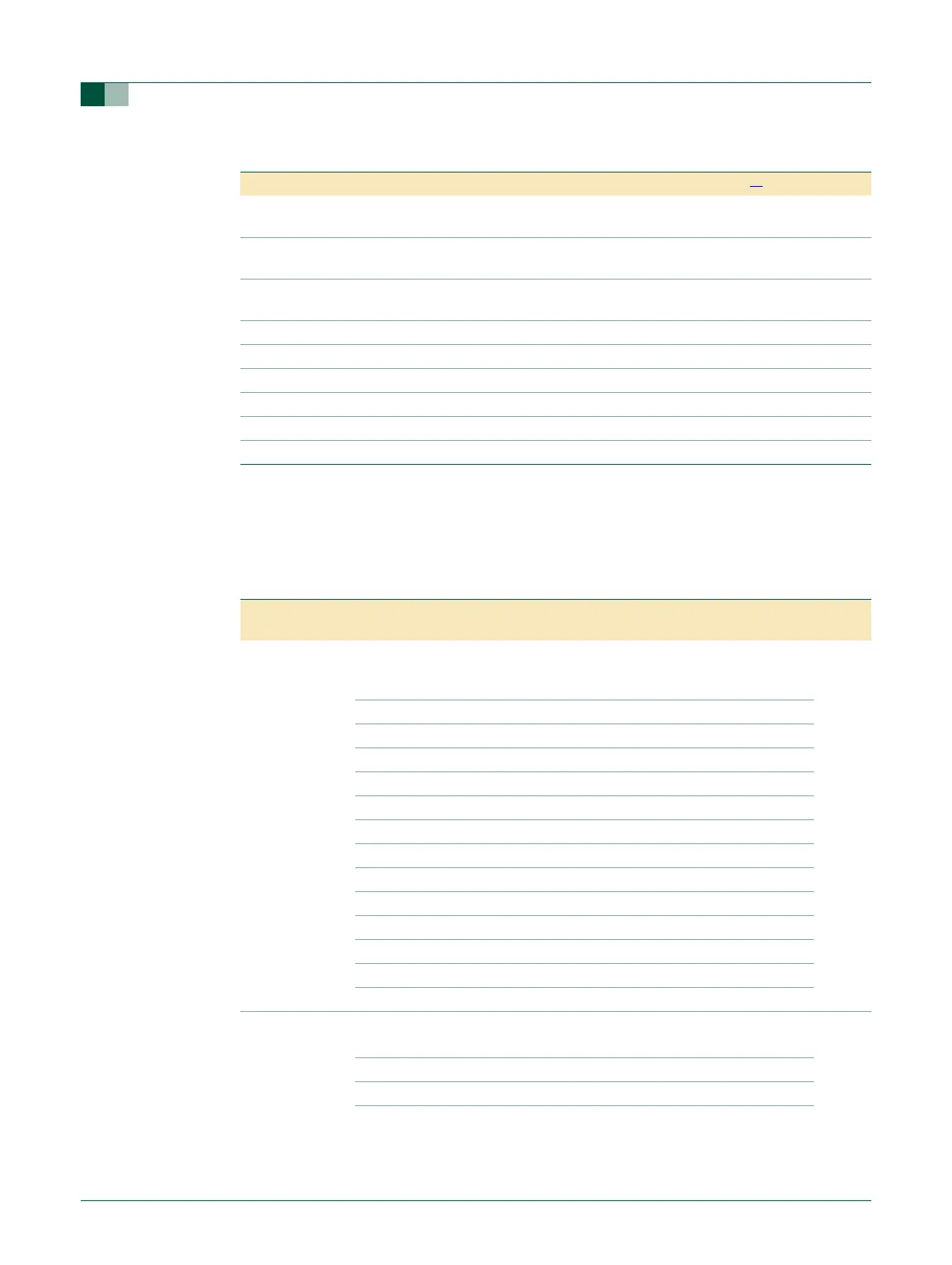

Table 148: SSP Control Register 0 (SSPCR0 - address 0xE006 8000) bit description

Bit Symbol Value Description Reset

value

3:0 DSS Data Size Select. This field controls the number of bits

transferred in each frame. Values 0000-0010 are not

supported and should not be used.

0000

0011 4 bit transfer

0100 5 bit transfer

0101 6 bit transfer

0110 7 bit transfer

0111 8 bit transfer

1000 9 bit transfer

1001 10 bit transfer

1010 11 bit transfer

1011 12 bit transfer

1100 13 bit transfer

1101 14 bit transfer

1110 15 bit transfer

1111 16 bit transfer

5:4 FRF

00

Frame Format.

SPI

00

01 SSI

10 Microwire

11 This combination is not supported and should not be used.

Loading...

Loading...