© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

User manual Rev. 01 — 12 January 2006 111

Philips Semiconductors

UM10161

Volume 1 Chapter 10: UART1

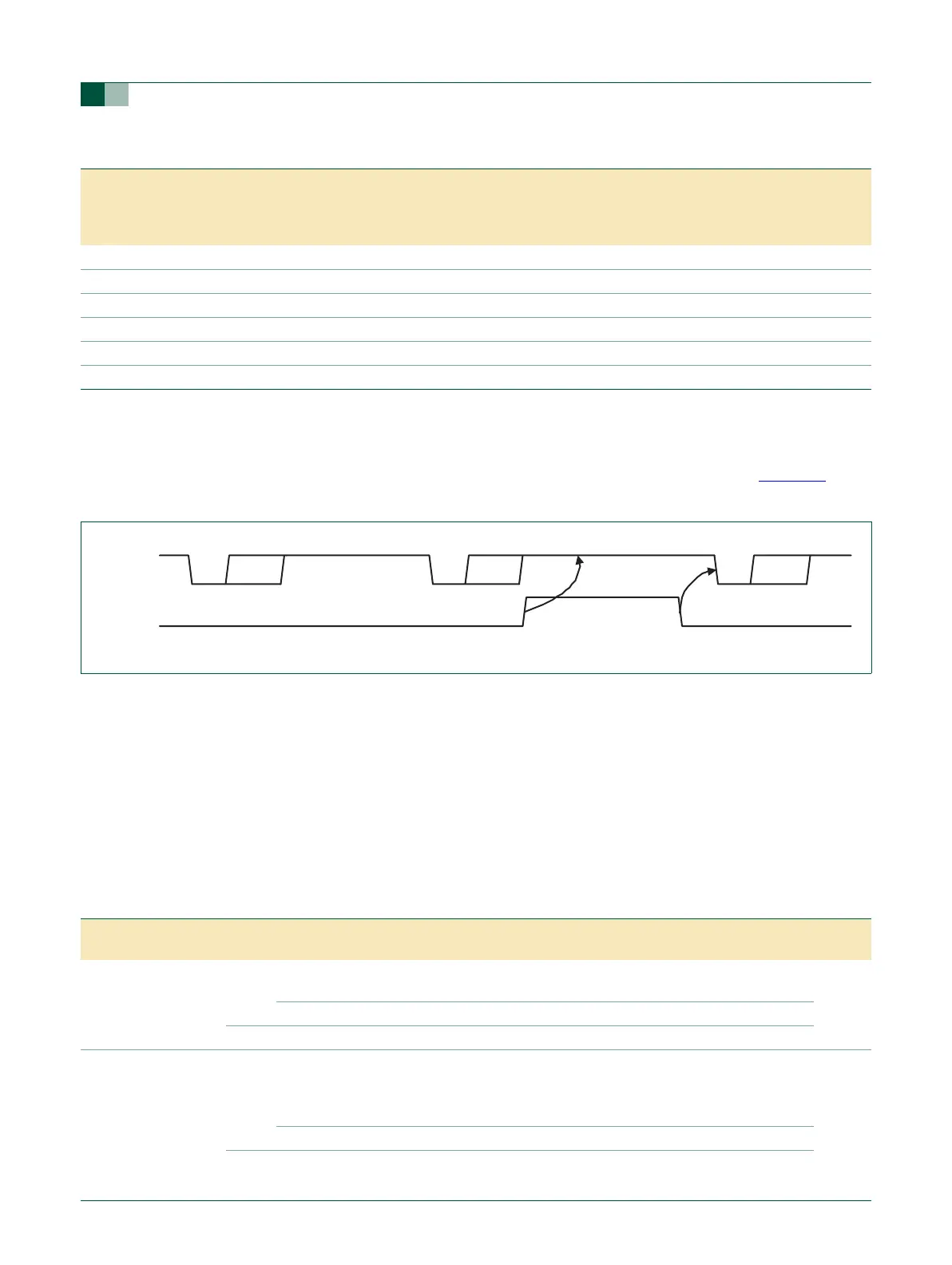

The auto-CTS function reduces interrupts to the host system. When flow control is

enabled, a CTS1 state change does not trigger host interrupts because the device

automatically controls its own transmitter. Without auto-CTS, the transmitter sends any

data present in the transmit FIFO and a receiver overrun error can result. Figure 20

illustrates the auto-CTS functional timing.

While starting transmission of the initial character the CTS1 signal is asserted.

Transmission will stall as soon as the pending transmission has completed. The UART will

continue transmitting a 1 bit as long as CTS1 is deasserted (HIGH). As soon as CTS1

gets deasserted transmission resumes and a start bit is sent followed by the data bits of

the next character.

10.3.11 UART1 Line Status Register (U1LSR - 0xE001 0014, Read Only)

The U1LSR is a read-only register that provides status information on the UART1 TX and

RX blocks.

10xx1 yes

110x0 no

110x1 yes

11100 no

1111x yes

111x1 yes

Table 111: Modem status interrupt generation

Enable Modem

Status

Interrupt

(U1IER[3])

CTSen

(U1MCR[7])

CTS Interrupt

Enable

(U1IER[7])

Delta CTS

(U1MSR[0])

Delta DCD or

Trailing Edge RI or

Delta DSR

(U1MSR[3] or U1MSR[2] or (U1MSR[1]))

Modem Status

Interrupt

Fig 20. Auto-CTS functional timing

start bits0..7 start bits0..7 stop start bits0..7 stop

UART1 Tx

CTS1 pin

~

~

~

~

~

~

~

~

stop

Table 112: UART1 Line Status Register (U1LSR - address 0xE001 0014, read only) bit description

Bit Symbol Value Description Reset

value

0 Receiver Data

Ready

(RDR)

0

U1LSR[0] is set when the U1RBR holds an unread character and is cleared when

the UART1 RBR FIFO is empty.

0

U1RBR is empty.

1 U1RBR contains valid data.

1 Overrun Error

(OE)

0

The overrun error condition is set as soon as it occurs. An U1LSR read clears

U1LSR[1]. U1LSR[1] is set when UART1 RSR has a new character assembled and

the UART1 RBR FIFO is full. In this case, the UART1 RBR FIFO will not be

overwritten and the character in the UART1 RSR will be lost.

0

Overrun error status is inactive.

1 Overrun error status is active.

Loading...

Loading...