© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

User manual Rev. 01 — 12 January 2006 227

Philips Semiconductors

UM10161

Volume 1 Chapter 18: WDT

18.4.2 Watchdog Timer Constant register (WDTC - 0xE000 0004)

The WDTC register determines the time-out value. Every time a feed sequence occurs the

WDTC content is reloaded in to the watchdog timer. It’s a 32-bit register with 8 LSB set to

1 on reset. Writing values below 0xFF will cause 0xFF to be loaded to the WDTC. Thus

the minimum time-out interval is T

PCLK

× 256 × 4.

18.4.3 Watchdog Feed register (WDFEED - 0xE000 0008)

Writing 0xAA followed by 0x55 to this register will reload the watchdog timer to the WDTC

value. This operation will also start the watchdog if it is enabled via the WDMOD register.

Setting the WDEN bit in the WDMOD register is not sufficient to enable the watchdog. A

valid feed sequence must first be completed before the watchdog is capable of generating

an interrupt/reset. Until then, the watchdog will ignore feed errors. Once 0xAA is written to

the WDFEED register the next operation in the watchdog register space should be a

WRITE (0x55) to the WDFFED register otherwise the watchdog is triggered. The

interrupt/reset will be generated during the second PCLK following an incorrect access to

a watchdog timer register during a feed sequence.

18.4.4 Watchdog Timer Value register (WDTV - 0xE000 000C)

The WDTV register is used to read the current value of watchdog timer.

18.5 Block diagram

The block diagram of the Watchdog is shown below in the Figure 60.

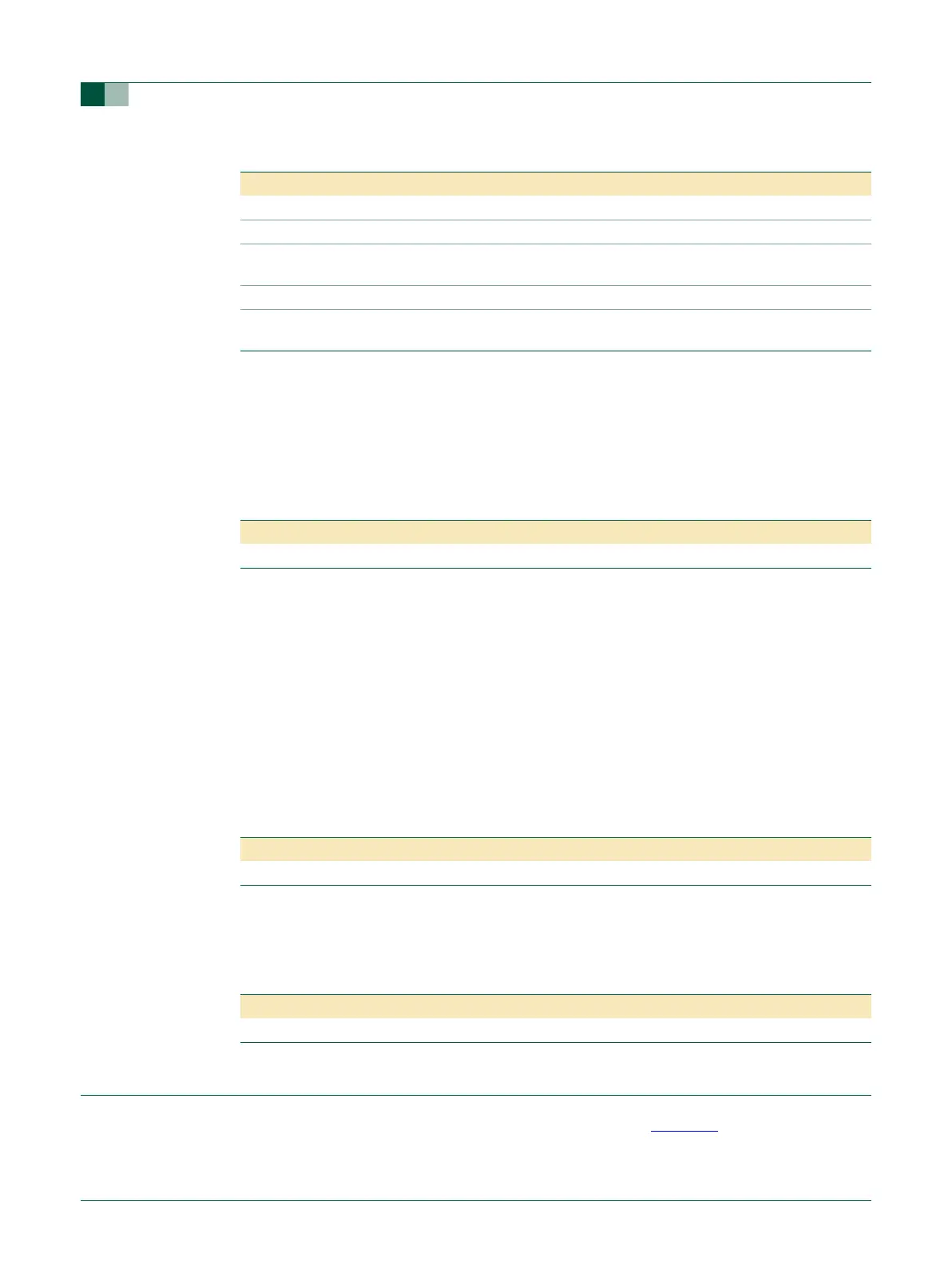

Table 204: Watchdog Mode register (WDMOD - address 0xE000 0000) bit description

Bit Symbol Description Reset value

0 WDEN WDEN Watchdog interrupt Enable bit (Set Only). 0

1 WDRESET WDRESET Watchdog Reset Enable bit (Set Only). 0

2 WDTOF WDTOF Watchdog Time-Out Flag. 0 (Only after

external reset)

3 WDINT WDINT Watchdog interrupt Flag (Read Only). 0

7:4 - Reserved, user software should not write ones to reserved

bits. The value read from a reserved bit is not defined.

NA

Table 205: Watchdog Timer Constant register (WDTC - address 0xE000 0004) bit description

Bit Symbol Description Reset value

31:0 Count Watchdog time-out interval. 0x0000 00FF

Table 206: Watchdog Feed register (WDFEED - address 0xE000 0008) bit description

Bit Symbol Description Reset value

7:0 Feed Feed value should be 0xAA followed by 0x55. NA

Table 207: Watchdog Timer Value register (WDTV - address 0xE000 000C) bit description

Bit Symbol Description Reset value

31:0 Count Counter timer value. 0x0000 00FF

Loading...

Loading...