© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

User manual Rev. 01 — 12 January 2006 51

Philips Semiconductors

UM10161

Volume 1 Chapter 5: VIC

5.4.8 FIQ Status register (VICFIQStatus - 0xFFFF F004)

This is a read only register. This register reads out the state of those interrupt requests

that are enabled and classified as FIQ. If more than one request is classified as FIQ, the

FIQ service routine can read this register to see which request(s) is (are) active.

5.4.9 Vector Control registers 0-15 (VICVectCntl0-15 - 0xFFFF F200-23C)

These are a read/write accessible registers. Each of these registers controls one of the 16

vectored IRQ slots. Slot 0 has the highest priority and slot 15 the lowest. Note that

disabling a vectored IRQ slot in one of the VICVectCntl registers does not disable the

interrupt itself, the interrupt is simply changed to the non-vectored form.

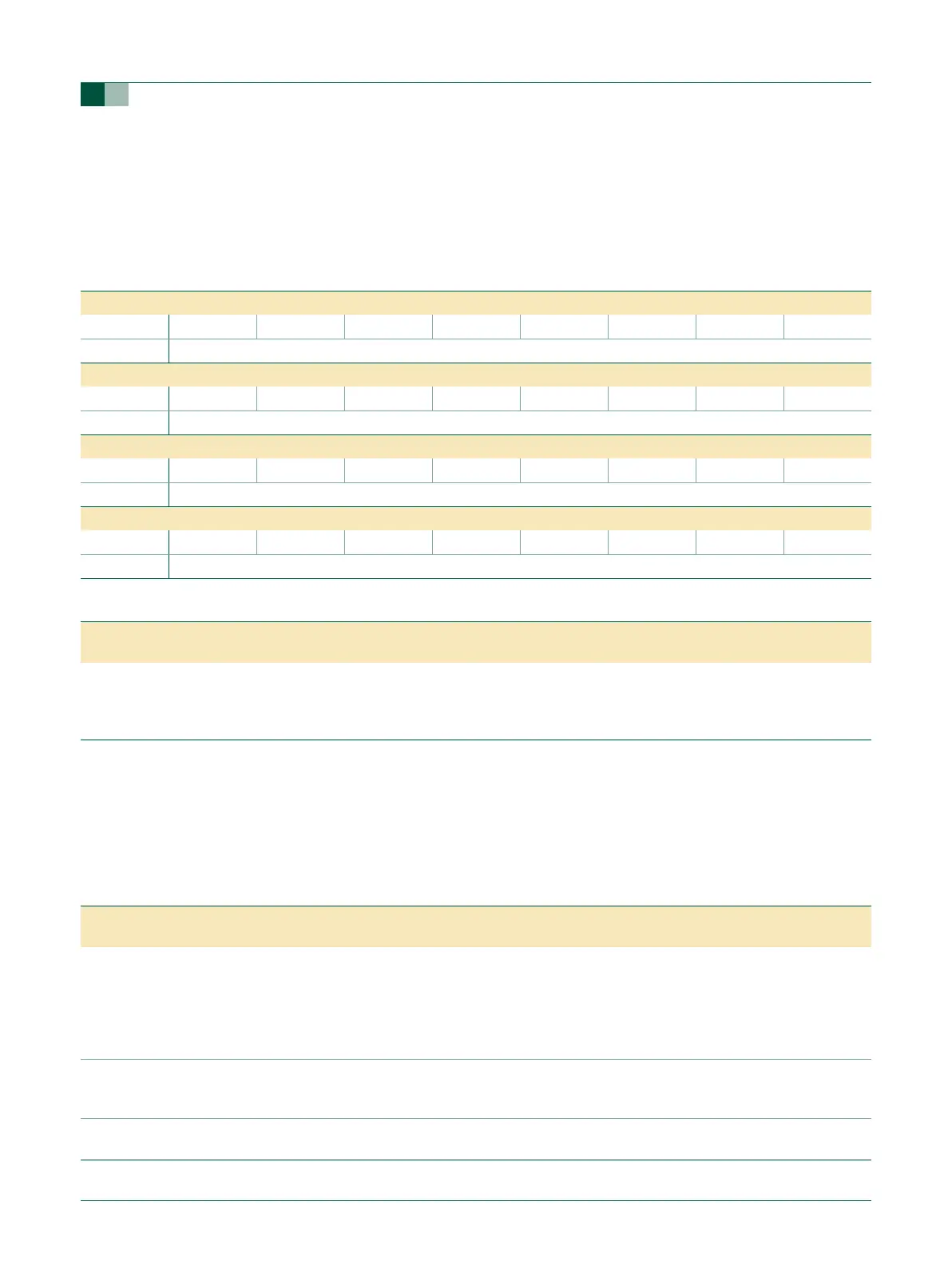

Table 50: FIQ Status register (VICFIQStatus - address 0xFFFF F004) bit allocation

Reset value: 0x0000 0000

Bit 31 30 29 28 27 26 25 24

Symbol ----TIMER3TIMER2--

Access RO RO RO RO RO RO RO RO

Bit 23 22 21 20 19 18 17 16

Symbol ----I2C1AD0-EINT2

Access RO RO RO RO RO RO RO RO

Bit 15 14 13 12 11 10 9 8

Symbol EINT1 EINT0 RTC PLL SSP/SPI1 SPI0 I2C0 -0

Access RO RO RO RO RO RO RO RO

Bit 7 6 5 4 3 2 1 0

Symbol UART1 UART0 TIMER1 TIMER0 ARMCore1 ARMCore0 - WDT

Access RO RO RO RO RO RO RO RO

Table 51: FIQ Status register (VICFIQStatus - address 0xFFFF F004) bit description

Bit Symbol Description Reset

value

31:0 See

VICFIQStatus

bit allocation

table.

A bit read as 1 indicates a corresponding interrupt request being enabled,

classified as FIQ, and asserted

0

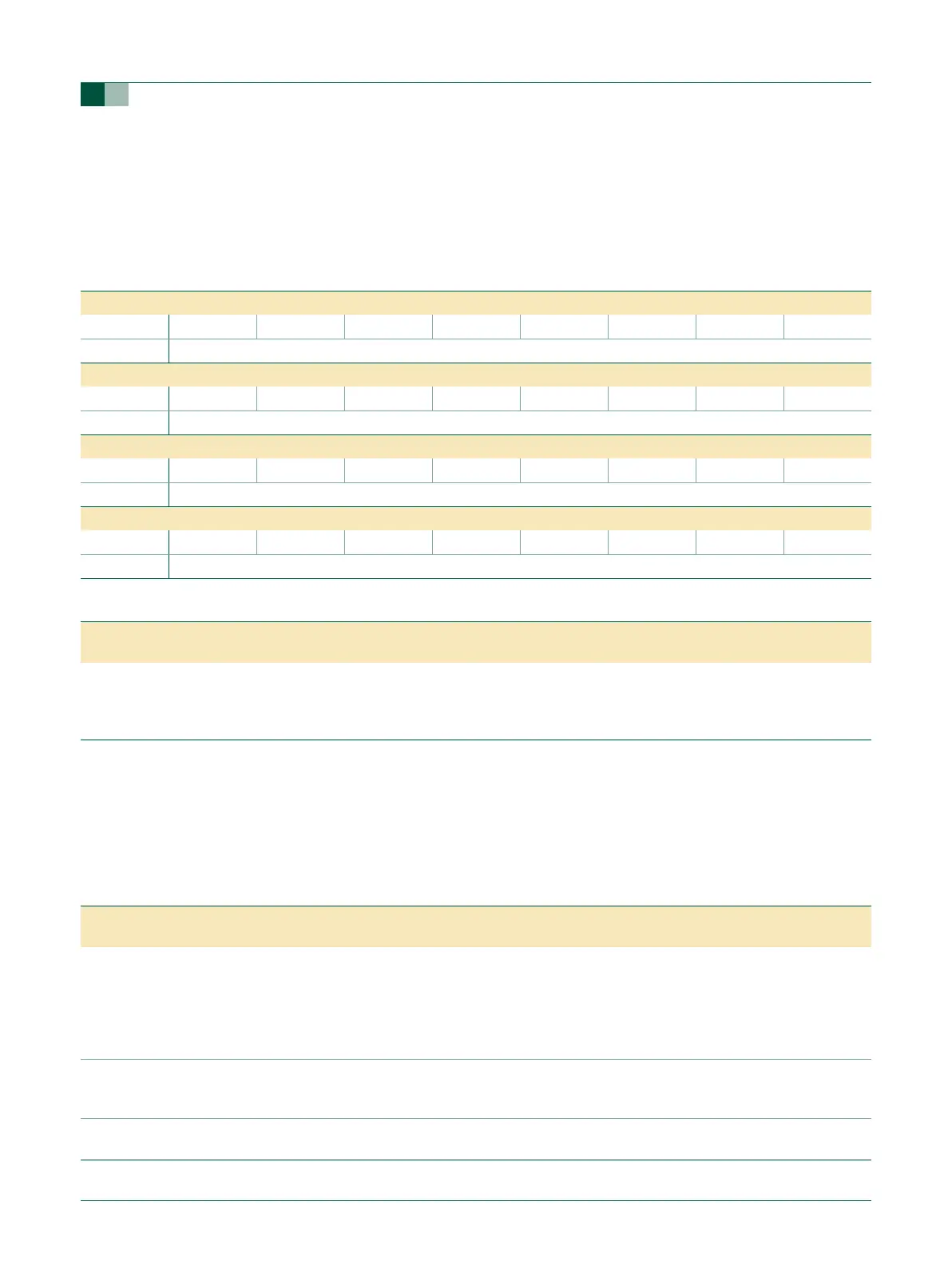

Table 52: Vector Control registers 0-15 (VICVectCntl0-15 - 0xFFFF F200-23C) bit description

Bit Symbol Description Reset

value

4:0 int_request/

sw_int_assig

The number of the interrupt request or software interrupt assigned to this

vectored IRQ slot. As a matter of good programming practice, software should

not assign the same interrupt number to more than one enabled vectored IRQ

slot. But if this does occur, the lower numbered slot will be used when the

interrupt request or software interrupt is enabled, classified as IRQ, and

asserted.

0

5 IRQslot_en When 1, this vectored IRQ slot is enabled, and can produce a unique ISR

address when its assigned interrupt request or software interrupt is enabled,

classified as IRQ, and asserted.

0

31:6 - Reserved, user software should not write ones to reserved bits. The value read

from a reserved bit is not defined.

NA

Loading...

Loading...