© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

User manual Rev. 01 — 12 January 2006 217

Philips Semiconductors

UM10161

Volume 1 Chapter 17: RTC

17.4.7 Alarm Mask Register (AMR - 0xE002 4010)

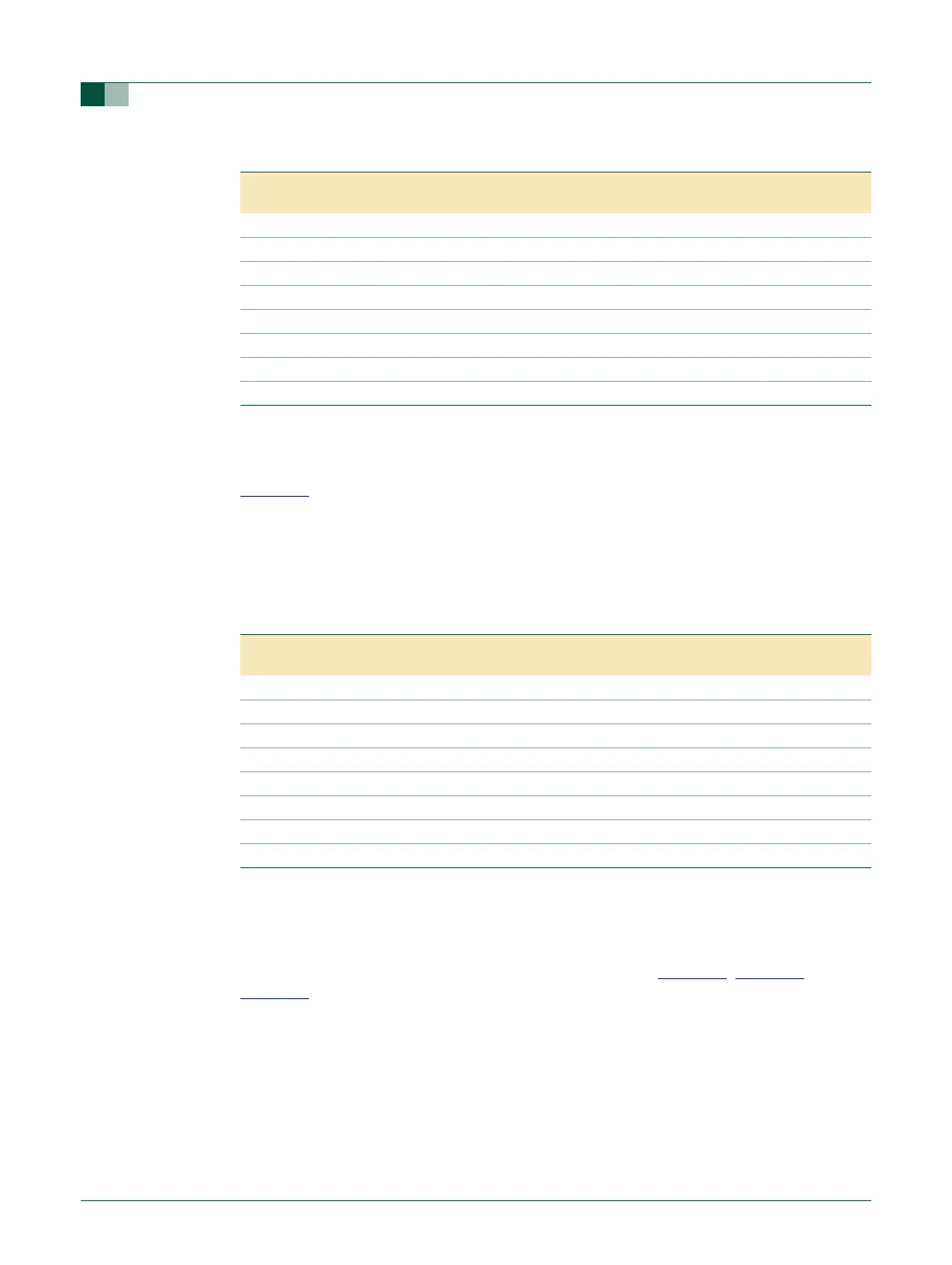

The Alarm Mask Register (AMR) allows the user to mask any of the alarm registers.

Table 190

shows the relationship between the bits in the AMR and the alarms. For the

alarm function, every non-masked alarm register must match the corresponding time

counter for an interrupt to be generated. The interrupt is generated only when the counter

comparison first changes from no match to match. The interrupt is removed when a one is

written to the appropriate bit of the Interrupt Location Register (ILR). If all mask bits are

set, then the alarm is disabled.

17.4.8 Consolidated time registers

The values of the Time Counters can optionally be read in a consolidated format which

allows the programmer to read all time counters with only three read operations. The

various registers are packed into 32-bit values as shown in Table 191

, Table 192, and

Table 193

. The least significant bit of each register is read back at bit 0, 8, 16, or 24.

The Consolidated Time Registers are read only. To write new values to the Time

Counters, the Time Counter addresses should be used.

17.4.9 Consolidated Time register 0 (CTIME0 - 0xE002 4014)

The Consolidated Time Register 0 contains the low order time values: Seconds, Minutes,

Hours, and Day of Week.

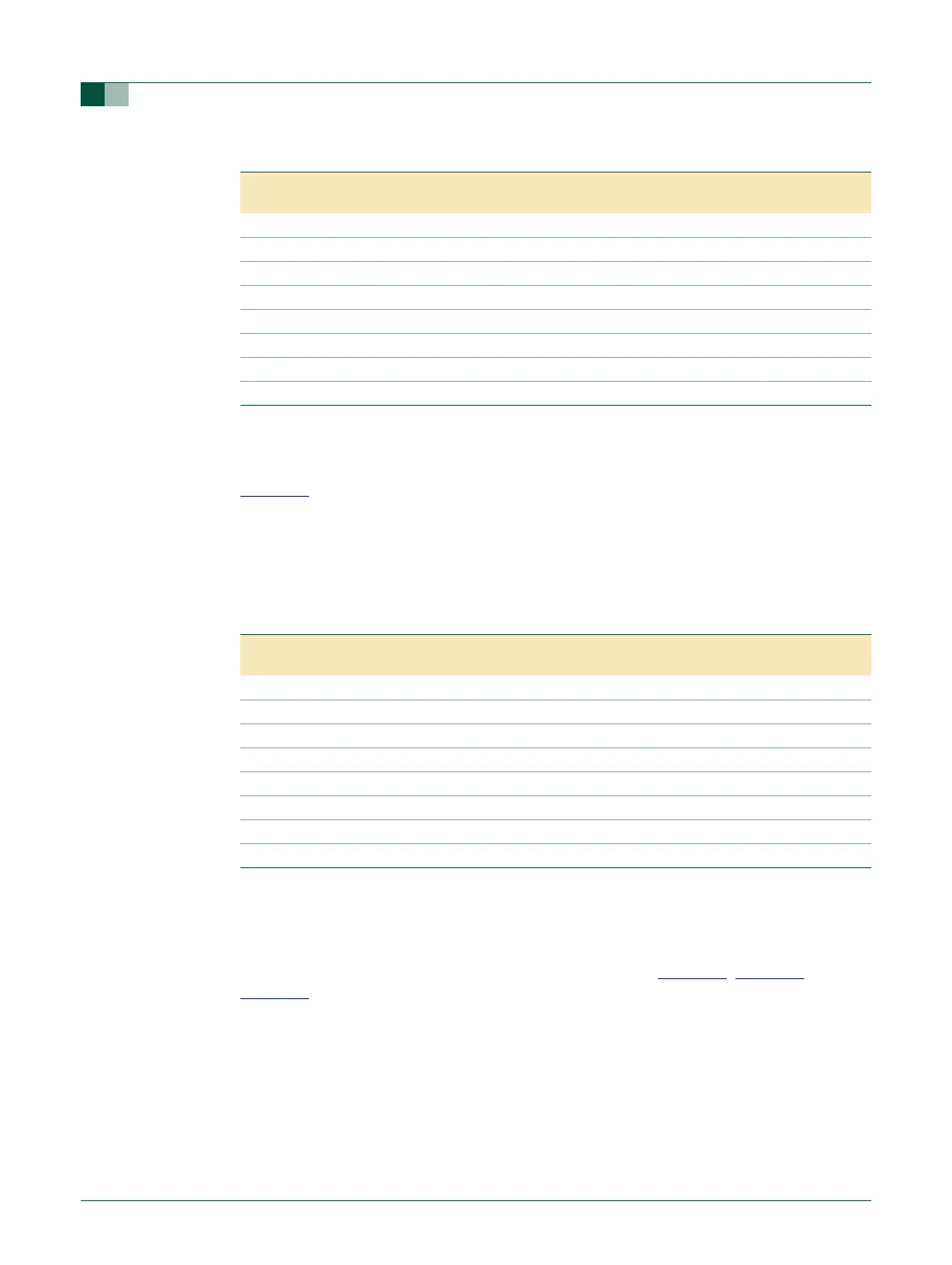

Table 189: Counter Increment Interrupt Register (CIIR - address 0xE002 400C) bit description

Bit Symbol Description Reset

value

0 IMSEC When 1, an increment of the Second value generates an interrupt. NA

1 IMMIN When 1, an increment of the Minute value generates an interrupt. NA

2 IMHOUR When 1, an increment of the Hour value generates an interrupt. NA

3 IMDOM When 1, an increment of the Day of Month value generates an interrupt. NA

4 IMDOW When 1, an increment of the Day of Week value generates an interrupt. NA

5 IMDOY When 1, an increment of the Day of Year value generates an interrupt. NA

6 IMMON When 1, an increment of the Month value generates an interrupt. NA

7 IMYEAR When 1, an increment of the Year value generates an interrupt. NA

Table 190: Alarm Mask Register (AMR - address 0xE002 4010) bit description

Bit Symbol Description Reset

value

0 AMRSEC When 1, the Second value is not compared for the alarm. NA

1 AMRMIN When 1, the Minutes value is not compared for the alarm. NA

2 AMRHOUR When 1, the Hour value is not compared for the alarm. NA

3 AMRDOM When 1, the Day of Month value is not compared for the alarm. NA

4 AMRDOW When 1, the Day of Week value is not compared for the alarm. NA

5 AMRDOY When 1, the Day of Year value is not compared for the alarm. NA

6 AMRMON When 1, the Month value is not compared for the alarm. NA

7 AMRYEAR When 1, the Year value is not compared for the alarm. NA

Loading...

Loading...