© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

User manual Rev. 01 — 12 January 2006 108

Philips Semiconductors

UM10161

Volume 1 Chapter 10: UART1

10.3.9 UART1 Line Control Register (U1LCR - 0xE001 000C)

The U1LCR determines the format of the data character that is to be transmitted or

received.

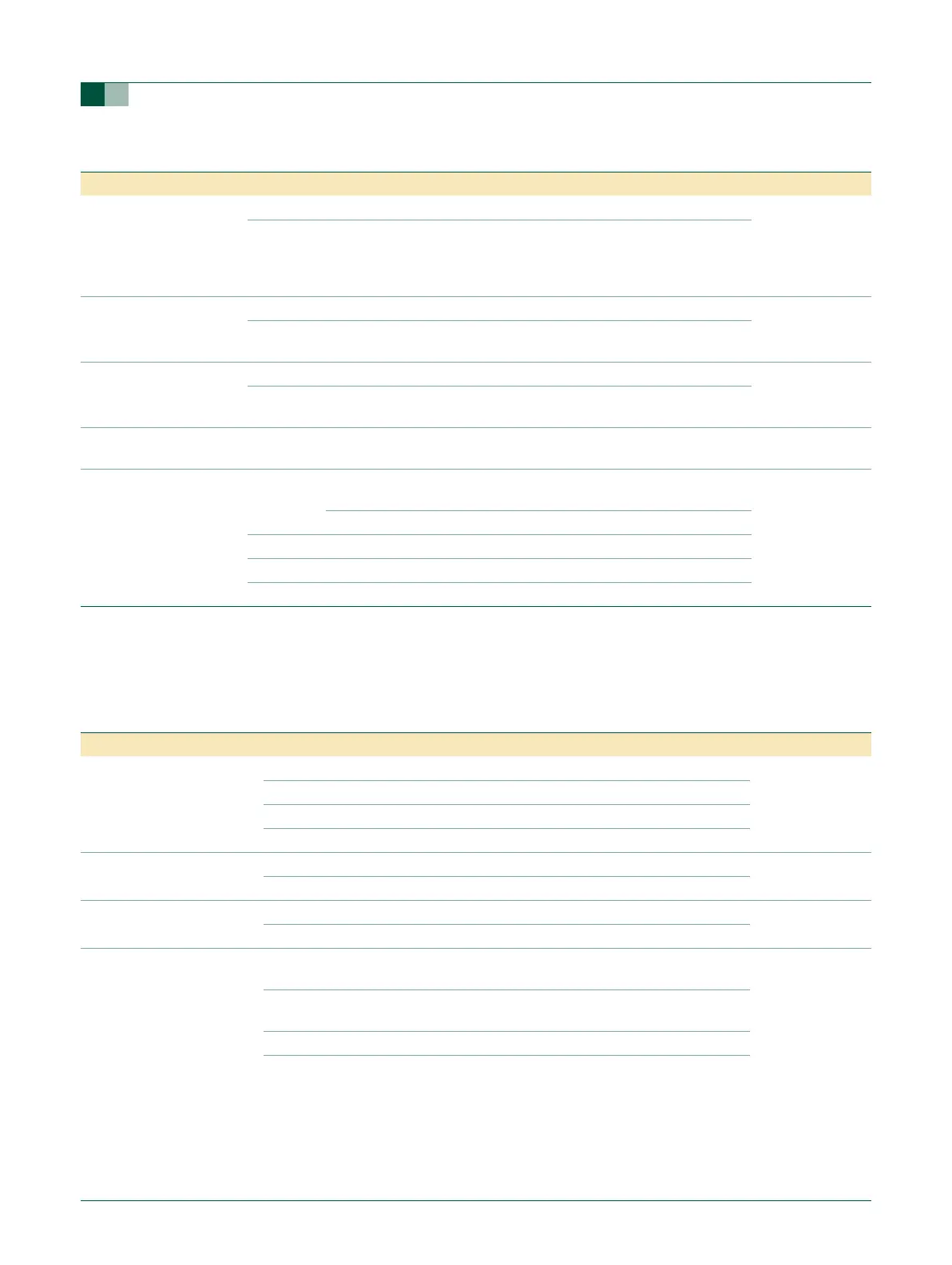

Table 108: UART1 FIFO Control Register (U1FCR - address 0xE001 0008) bit description

Bit Symbol Value Description Reset value

0 FIFO Enable 0 UART1 FIFOs are disabled. Must not be used in the application. 0

1 Active HIGH enable for both UART1 Rx and TX FIFOs and

U1FCR[7:1] access. This bit must be set for proper UART1

operation. Any transition on this bit will automatically clear the

UART1 FIFOs.

1 RX FIFO Reset 0 No impact on either of UART1 FIFOs. 0

1 Writing a logic 1 to U1FCR[1] will clear all bytes in UART1 Rx

FIFO and reset the pointer logic. This bit is self-clearing.

2 TX FIFO Reset 0 No impact on either of UART1 FIFOs. 0

1 Writing a logic 1 to U1FCR[2] will clear all bytes in UART1 TX

FIFO and reset the pointer logic. This bit is self-clearing.

5:3 - Reserved, user software should not write ones to reserved bits.

The value read from a reserved bit is not defined.

NA

7:6 RX Trigger Level

00

These two bits determine how many receiver UART1 FIFO

characters must be written before an interrupt is activated.

0

trigger level 0 (1 character or 0x01).

01 trigger level 1 (4 characters or 0x04).

10 trigger level 2 (8 characters or 0x08).

11 trigger level 3 (14 characters or 0x0E).

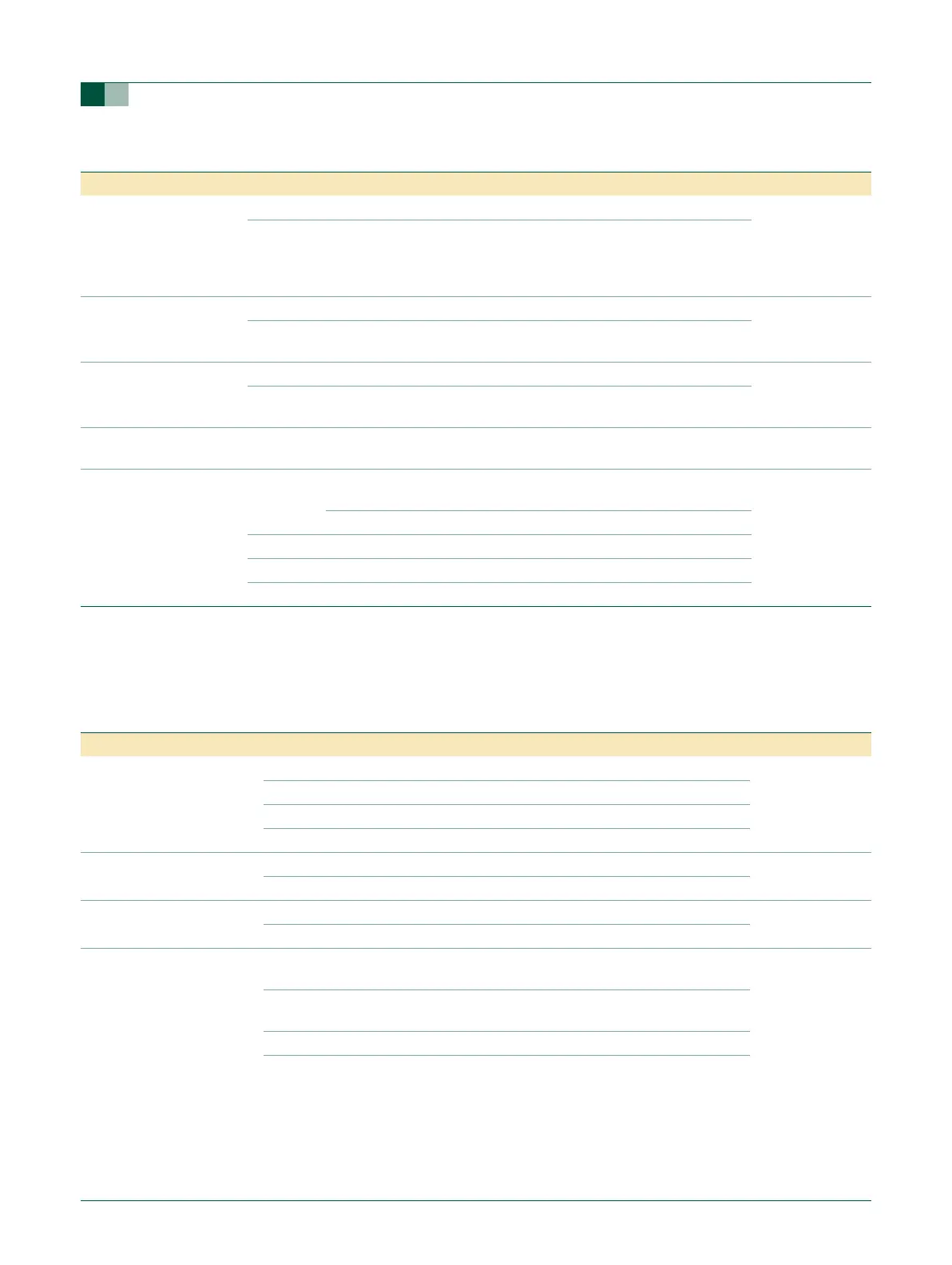

Table 109: UART1 Line Control Register (U1LCR - address 0xE001 000C) bit description

Bit Symbol Value Description Reset value

1:0 Word Length

Select

00 5 bit character length. 0

01 6 bit character length.

10 7 bit character length.

11 8 bit character length.

2 Stop Bit Select 0 1 stop bit. 0

1 2 stop bits (1.5 if U1LCR[1:0]=00).

3 Parity Enable 0 Disable parity generation and checking. 0

1 Enable parity generation and checking.

5:4 Parity Select 00 Odd parity. Number of 1s in the transmitted character and the

attached parity bit will be odd.

0

01 Even Parity. Number of 1s in the transmitted character and the

attached parity bit will be even.

10 Forced "1" stick parity.

11 Forced "0" stick parity.

Loading...

Loading...