© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

User manual Rev. 01 — 12 January 2006 87

Philips Semiconductors

UM10161

Volume 1 Chapter 9: UART0

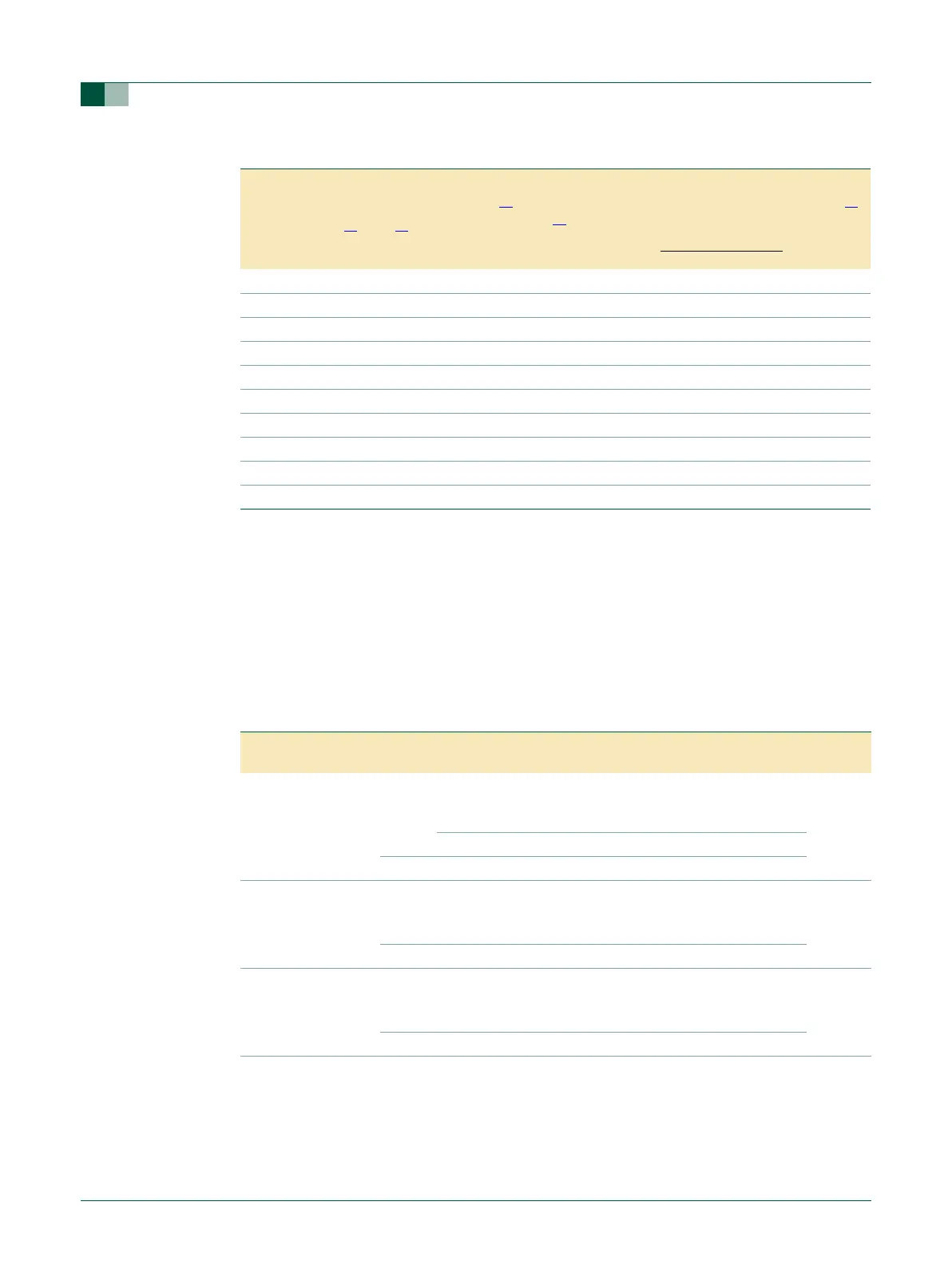

[1] Values in the row represent decimal equivalent of a 16 bit long content (DLM:DLL).

[2] Values in the row represent hex equivalent of a 16 bit long content (DLM:DLL).

[3] Refers to the percent error between desired and actual baudrate.

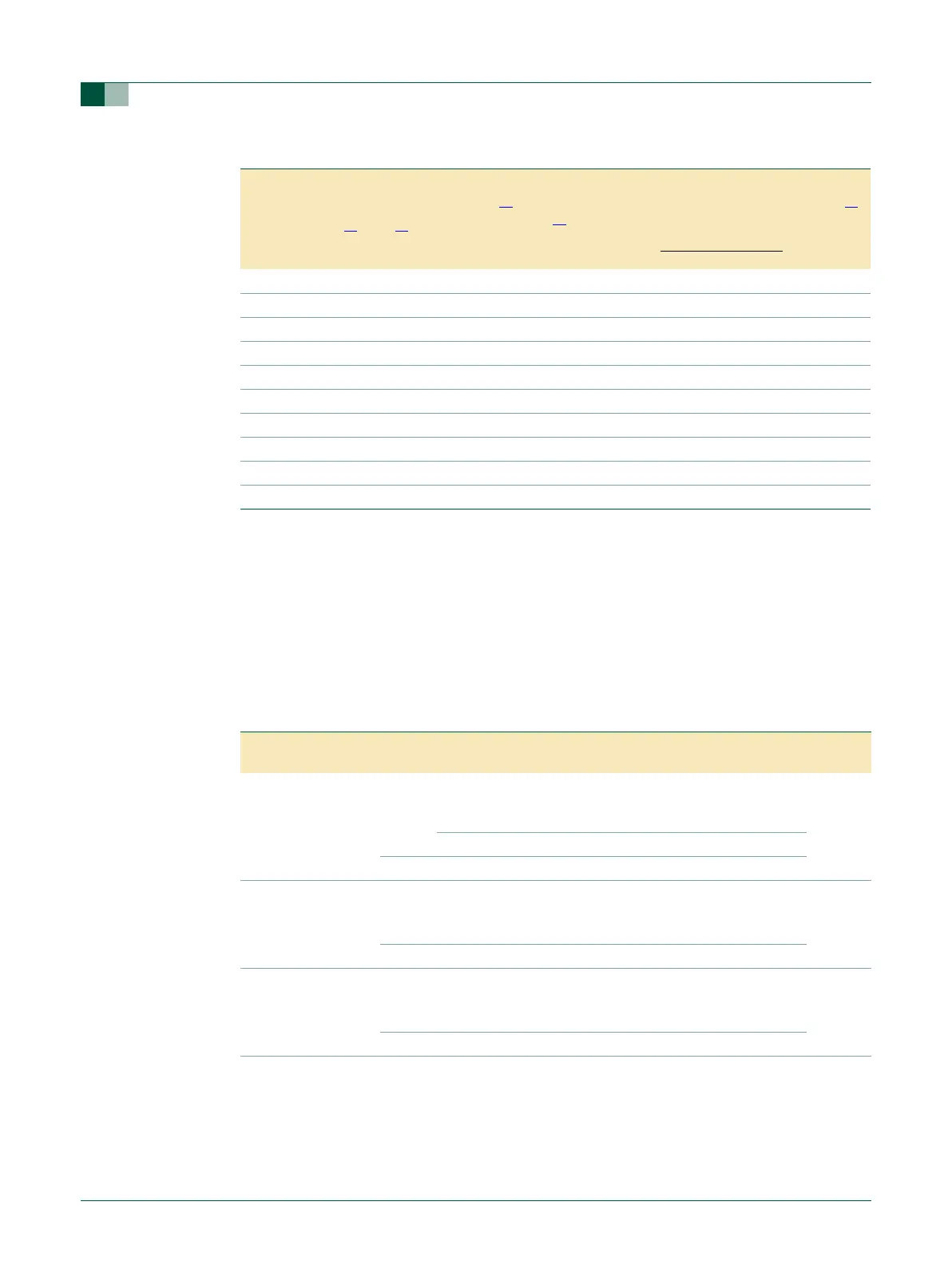

9.3.6 UART0 Interrupt Enable Register (U0IER - 0xE000 C004, when

DLAB = 0)

The U0IER is used to enable UART0 interrupt sources.

7200 00AE 174 0.2240 124 5/(5+2) 0.0064

9600 0082 130 0.1600 93 5/(5+2) 0.0064

19200 0041 65 0.1600 31 10/(10+11) 0.0064

38400 0021 33 1.3760 12 7/(7+12) 0.0594

56000 0021 22 1.4400 13 7/(7+5) 0.0160

57600 0016 22 1.3760 19 7/(7+1) 0.0594

112000 000B 11 1.4400 6 7/(7+6) 0.1600

115200 000B 11 1.3760 4 7/(7+12) 0.0594

224000 0006 6 7.5200 3 7/(7+6) 0.1600

448000 0003 3 7.5200 2 5/(5+2) 0.3520

Table 87: Baudrates available when using 20 MHz peripheral clock (PCLK = 20 MHz)

Desired

baudrate

MULVAL = 0 DIVADDVAL = 0 Optimal MULVAL & DIVADDVAL

U0DLM:U0DLL % error

[3]

U0DLM:U0DLL

dec

[1]

Fractional

pre-scaler value

MULDIV

MULDIV + DIVADDVAL

% error

[3]

hex

[2]

dec

[1]

Table 88: UART0 Interrupt Enable Register (U0IER - address 0xE000 C004, when DLAB = 0)

bit description

Bit Symbol Value Description Reset

value

0RBR

Interrupt

Enable

0

U0IER[0] enables the Receive Data Available interrupt

for UART0. It also controls the Character Receive

Time-out interrupt.

0

Disable the RDA interrupts.

1 Enable the RDA interrupts.

1THRE

Interrupt

Enable

0

U0IER[1] enables the THRE interrupt for UART0. The

status of this can be read from U0LSR[5].

Disable the THRE interrupts.

0

1 Enable the THRE interrupts.

2RX Line

Status

Interrupt

Enable

0

U0IER[2] enables the UART0 RX line status interrupts.

The status of this interrupt can be read from U0LSR[4:1].

Disable the RX line status interrupts.

0

1 Enable the RX line status interrupts.

7:3 - - Reserved, user software should not write ones to

reserved bits. The value read from a reserved bit is not

defined.

NA

Loading...

Loading...