Display Unit for F-CM(C)1 (Rev. 05), F-CM(C)REC1 (Rev. 01)

7

Document no. M1144956-003

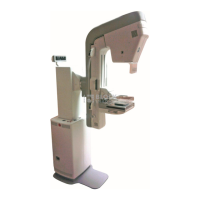

2.2 UPI section

The UPI functions as a general I/O section. It performs I/O duties assigned to it by the CPU. The

main processor and the processor on the UPI communicate through a dual-port memory

(shared RAM) which is located on the UPI section.

2.2.1 Functional Blocks

The UPI section contains the CPU bus interface, a processor, program and dual-port memories,

I/O block, and serial bus interface.

2.2.2 CPU Bus Interface

The UPI section is connected to the CPU section by CPU (ISA) bus. The following signals pass

between the UPI and CPU: data bus, address bus, reset, write and read signals.

2.2.3 Processor

The processor of the UPI section is a Hitachi H8S/2655, which functions at 16 MHz frequency.

2.2.4 Serial Bus Interface

The serial bus interface of the UPI section contains Module Bus RS485, serial RS232 and RS422

interfaces.

Figure 4 UPI Section Block Diagram

U

P

I

P

r

o

c

e

s

s

o

r

S

h

a

r

e

d

S

R

A

M

C

o

n

t

r

o

l

L

o

g

i

c

U

P

I

-

B

U

S

C

P

U

B

U

S

V

o

l

t

a

g

e

M

e

a

s

T

e

m

p

M

e

a

s

K

e

y

p

a

d

I

n

t

e

r

f

a

c

e

C

o

m

W

h

e

e

l

I

n

t

e

r

f

a

c

e

D

I

S

-

B

u

s

M

o

d

u

l

e

B

u

s

A

n

a

l

o

g

&

D

i

g

i

t

a

l

o

u

t

p

u

t

s

C

e

n

t

r

a

l

P

r

o

c

e

s

s

i

n

g

B

o

a

r

d

display_upi_diagr.vsd

Loading...

Loading...