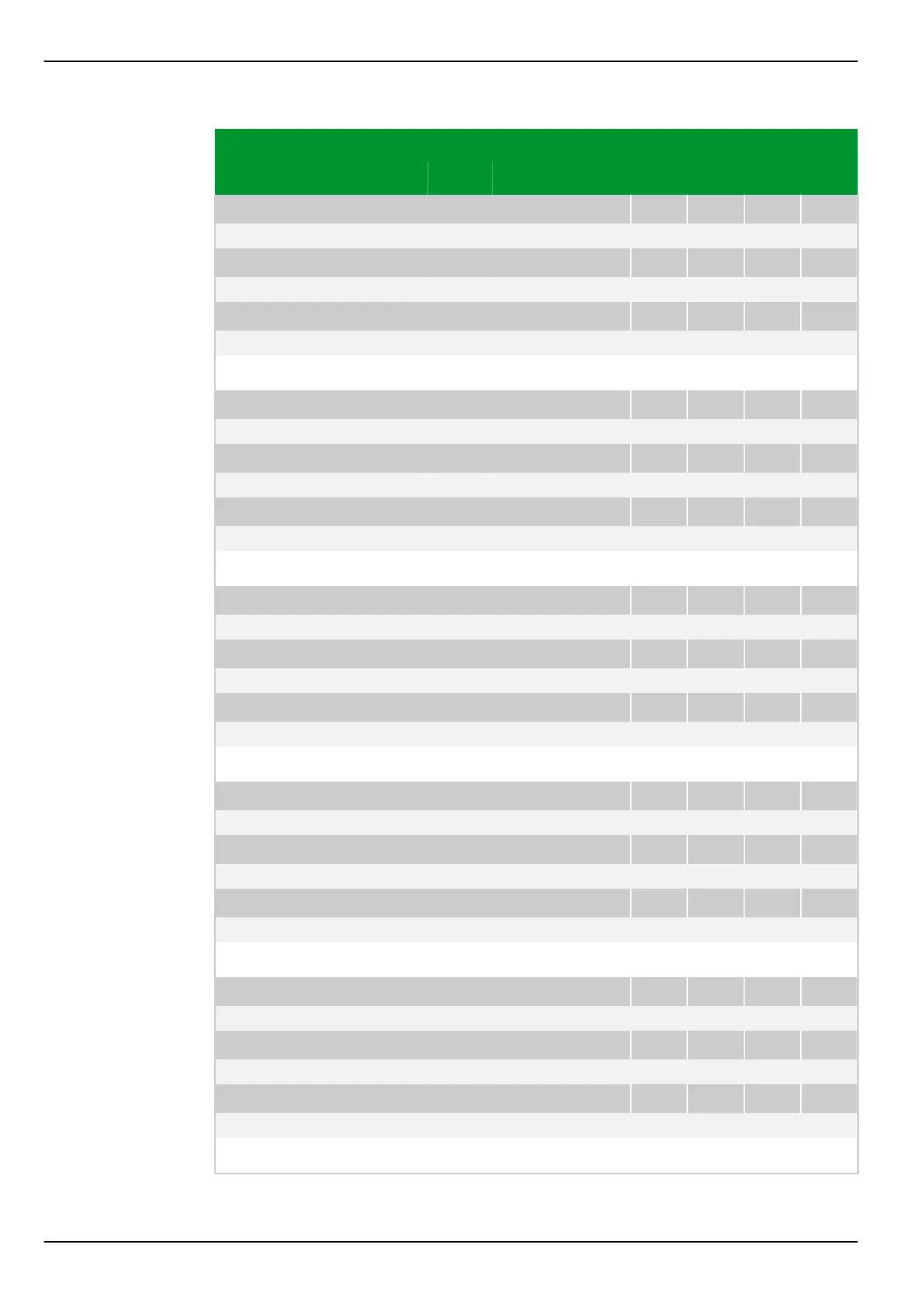

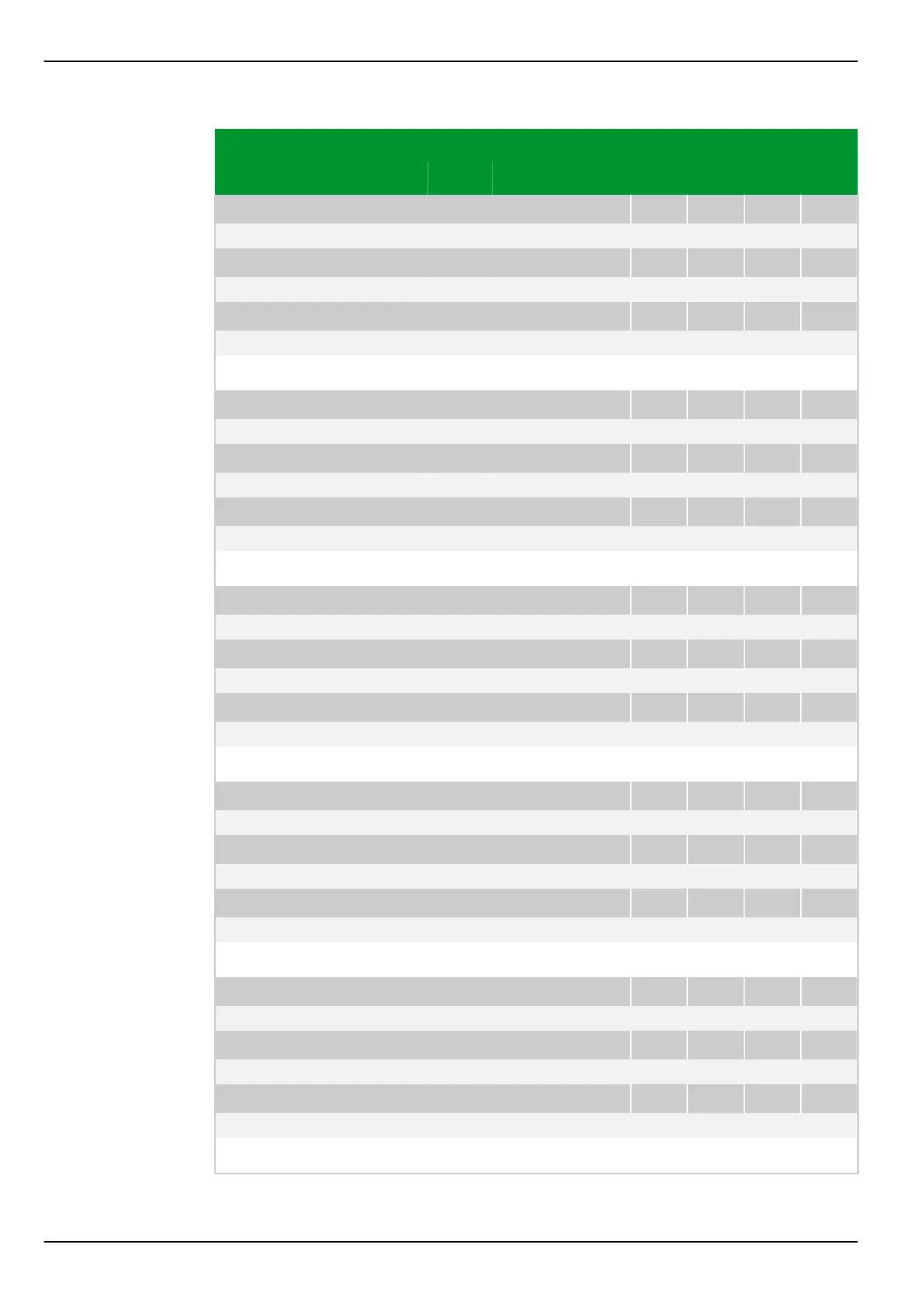

Parameter Address

Default Min Max Unit Logic Diagram

[spacer]

LIM_1: tI>>

015 121

Blocked 0 100 s Fig. 3-172, (p. 3-217)

[spacer]

LIM_2: tI>>

016 121

Blocked 0 100 s

[spacer]

LIM_3: tI>>

017 121

Blocked 0 100 s

[spacer]

Setting for the operate delay of I>>.

[spacer]

LIM_1: I<

015 118

0.10 0.00 4.00 Inom Fig. 3-172, (p. 3-217)

[spacer]

LIM_2: I<

016 118

0.10 0.00 4.00 Inom

[spacer]

LIM_3: I<

017 118

0.10 0.00 4.00 Inom

[spacer]

Setting for the operate value of I<.

[spacer]

LIM_1: I<<

015 119

Blocked 0.00 4.00 Inom Fig. 3-172, (p. 3-217)

[spacer]

LIM_2: I<<

016 119

Blocked 0.00 4.00 Inom

[spacer]

LIM_3: I<<

017 119

Blocked 0.00 4.00 Inom

[spacer]

Setting for the operate value of I<<.

[spacer]

LIM_1: tI<

015 122

5 0 100 s Fig. 3-172, (p. 3-217)

[spacer]

LIM_2: tI<

016 122

5 0 100 s

[spacer]

LIM_3: tI<

017 122

5 0 100 s

[spacer]

Setting for the operate delay of I<.

[spacer]

LIM_1: tI<<

015 123

Blocked 0 100 s Fig. 3-172, (p. 3-217)

[spacer]

LIM_2: tI<<

016 123

Blocked 0 100 s

[spacer]

LIM_3: tI<<

017 123

Blocked 0 100 s

[spacer]

Setting for the operate delay of I<<.

P634 7 Settings

7-102 P634/EN M/R-42-A // P634‑311‑653

Loading...

Loading...