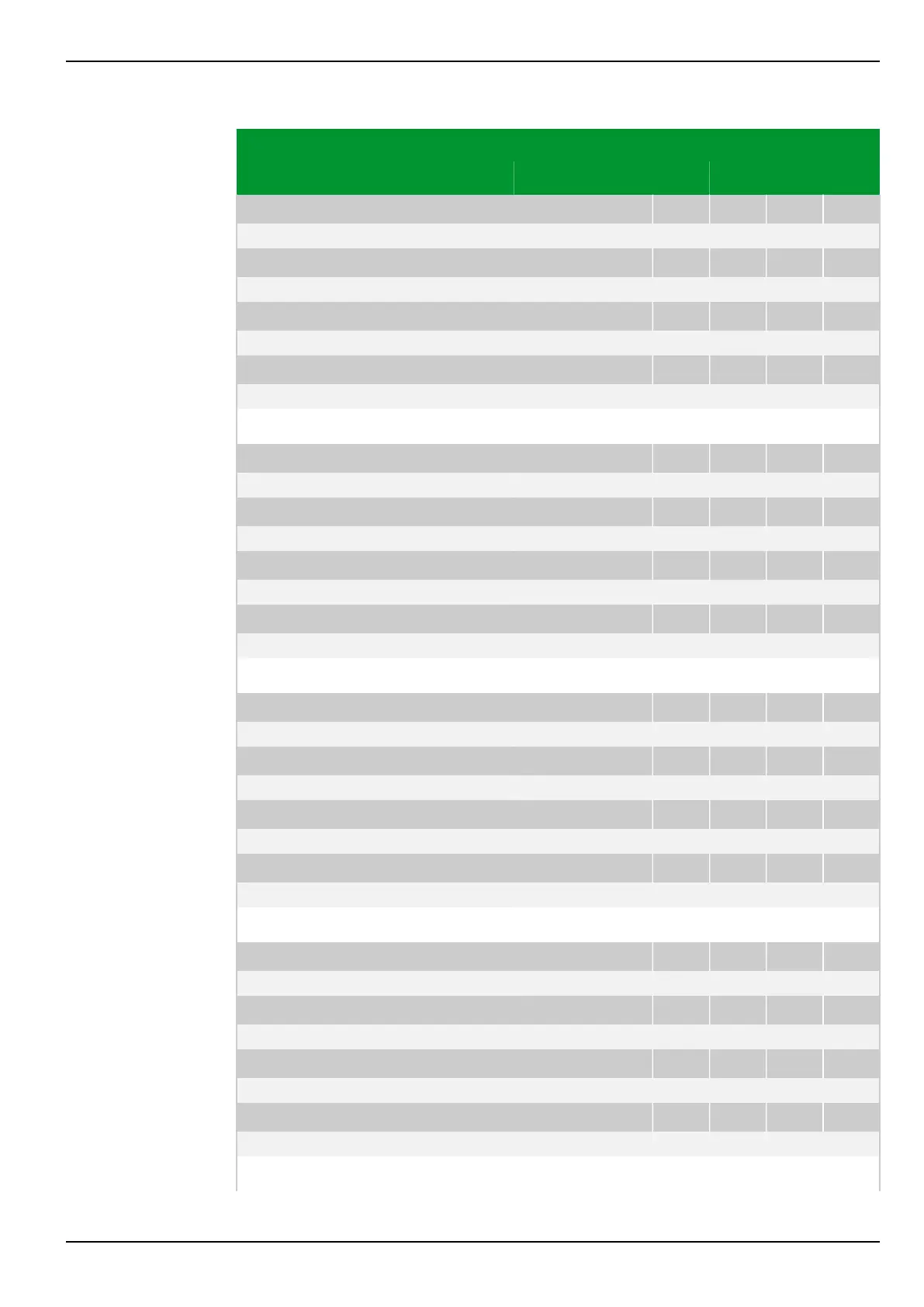

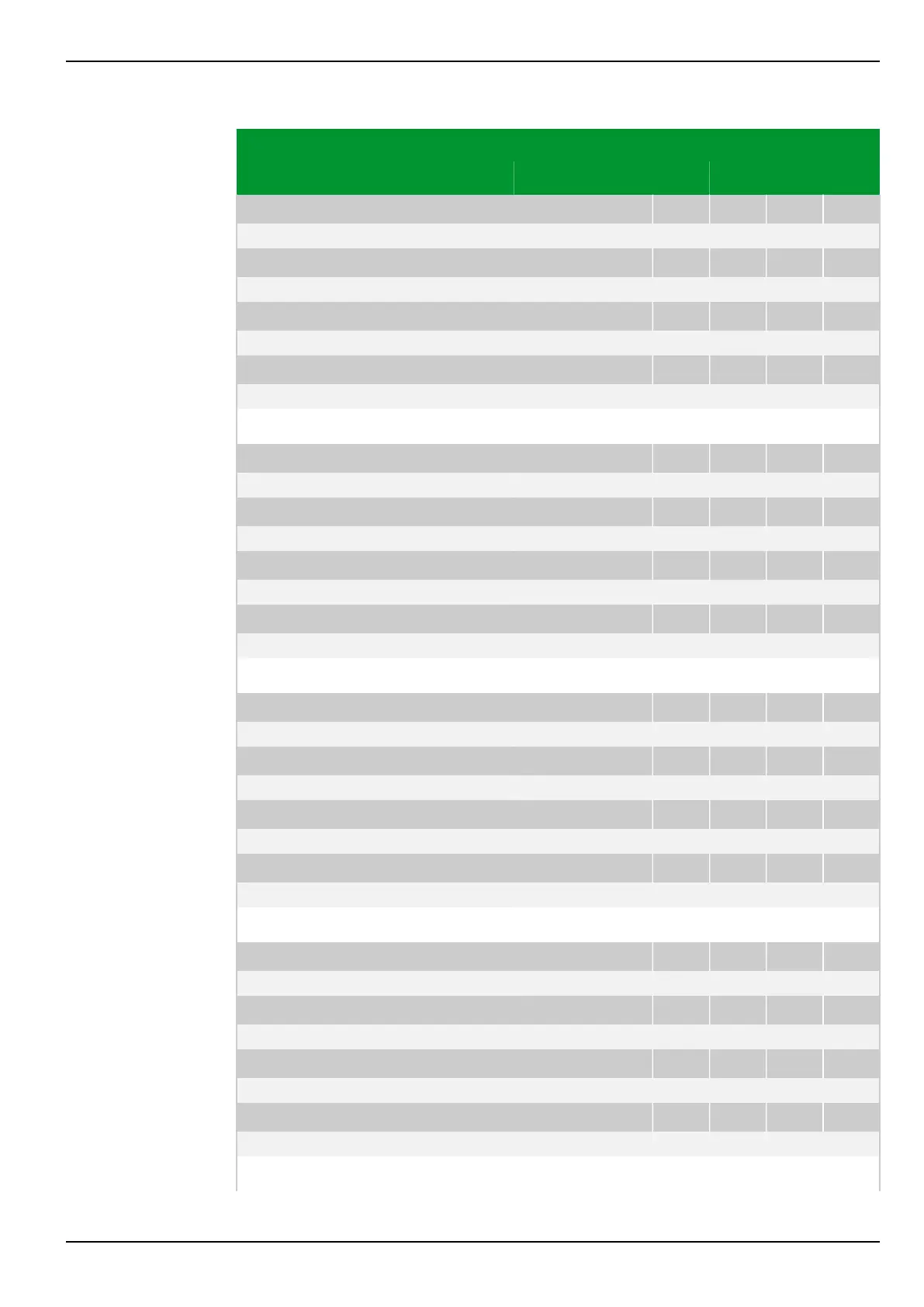

Parameter Address

Default Min Max Unit Logic Diagram

[spacer]

DTOC1: tI>> PSx

076 058 077 058 078 058 079 058

0.50 0.00 100.00 s Fig. 3-109, (p. 3-155)

[spacer]

DTOC2: tI>> PSx

076 078 077 078 078 078 079 078

0.50 0.00 100.00 s

[spacer]

DTOC3: tI>> PSx

076 188 077 188 078 188 079 188

0.50 0.00 100.00 s

[spacer]

DTOC4: tI>> PSx

099 092 099 093 099 094 099 095

0.50 0.00 100.00 s

[spacer]

Setting for operate delay I>>.

[spacer]

DTOC1: tI>>> PSx

076 059 077 059 078 059 079 059

0.50 0.00 100.00 s Fig. 3-109, (p. 3-155)

[spacer]

DTOC2: tI>>> PSx

076 169 077 169 078 169 079 169

0.50 0.00 100.00 s

[spacer]

DTOC3: tI>>> PSx

076 189 077 189 078 189 079 189

0.50 0.00 100.00 s

[spacer]

DTOC4: tI>>> PSx

099 096 099 097 099 098 099 099

0.50 0.00 100.00 s

[spacer]

Setting for the operate delay of the I>>> stage.

[spacer]

DTOC1: Ineg> PSx

076 197 077 197 078 197 079 197

0.25 0.10 8.00 Inom Fig. 3-110, (p. 3-156)

[spacer]

DTOC2: Ineg> PSx

076 207 077 207 078 207 079 207

0.25 0.10 8.00 Inom

[spacer]

DTOC3: Ineg> PSx

076 217 077 217 078 217 079 217

0.25 0.10 8.00 Inom

[spacer]

DTOC4: Ineg> PSx

099 164 099 165 099 166 099 167

0.25 0.10 8.00 Inom

[spacer]

Setting for the operate value of the Ineg> stage.

[spacer]

DTOC1: Ineg>> PSx

076 198 077 198 078 198 079 198

Blocked 0.10 8.00 Inom Fig. 3-110, (p. 3-156)

[spacer]

DTOC2: Ineg>> PSx

076 208 077 208 078 208 079 208

Blocked 0.10 8.00 Inom

[spacer]

DTOC3: Ineg>> PSx

076 218 077 218 078 218 079 218

Blocked 0.10 8.00 Inom

[spacer]

DTOC4: Ineg>> PSx

099 168 099 169 099 170 099 171

Blocked 0.10 8.00 Inom

[spacer]

Setting for the operate value of the Ineg>> stage.

7 Settings P634

P634/EN M/R-42-A // P634‑311‑653 7-161

Loading...

Loading...