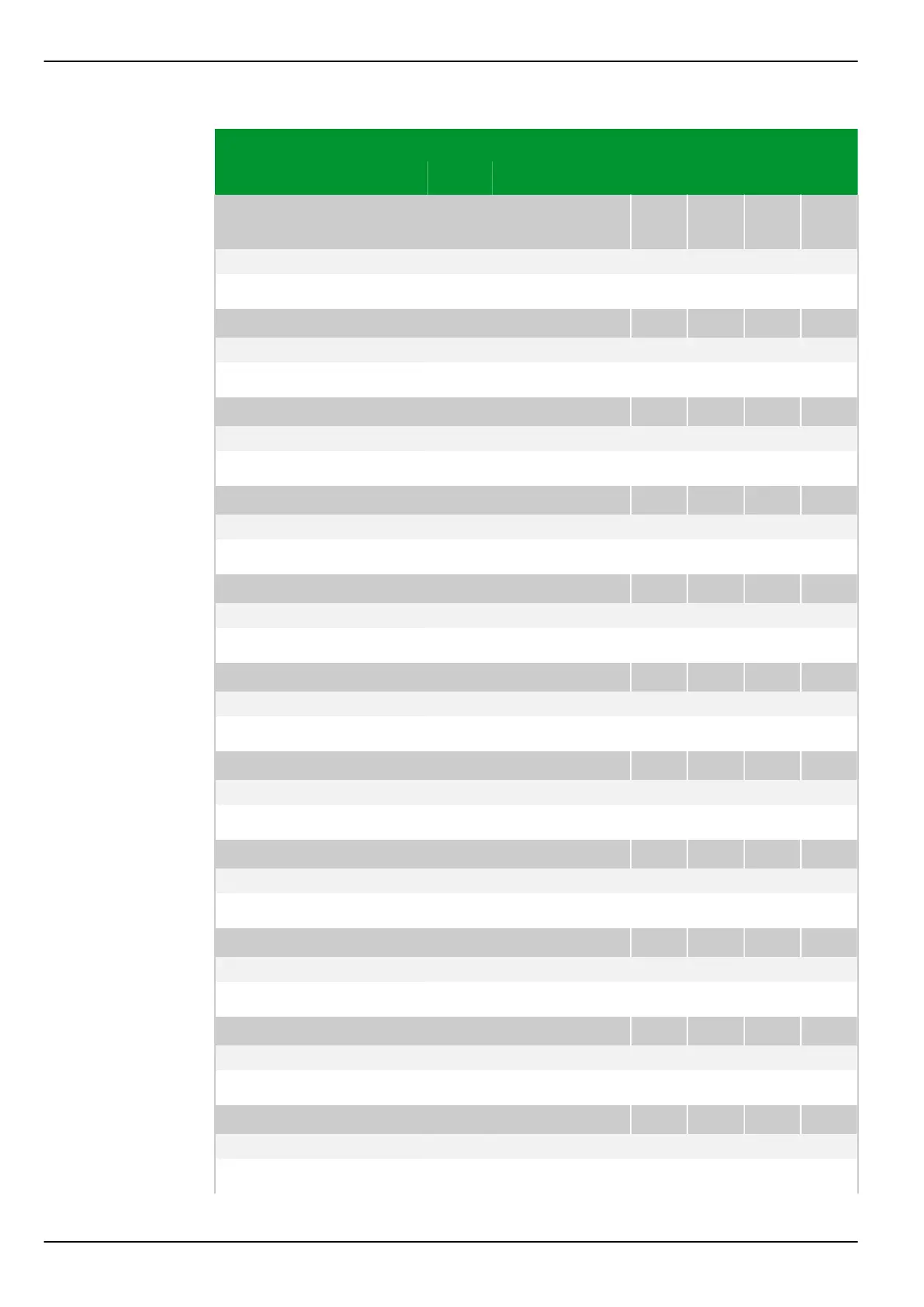

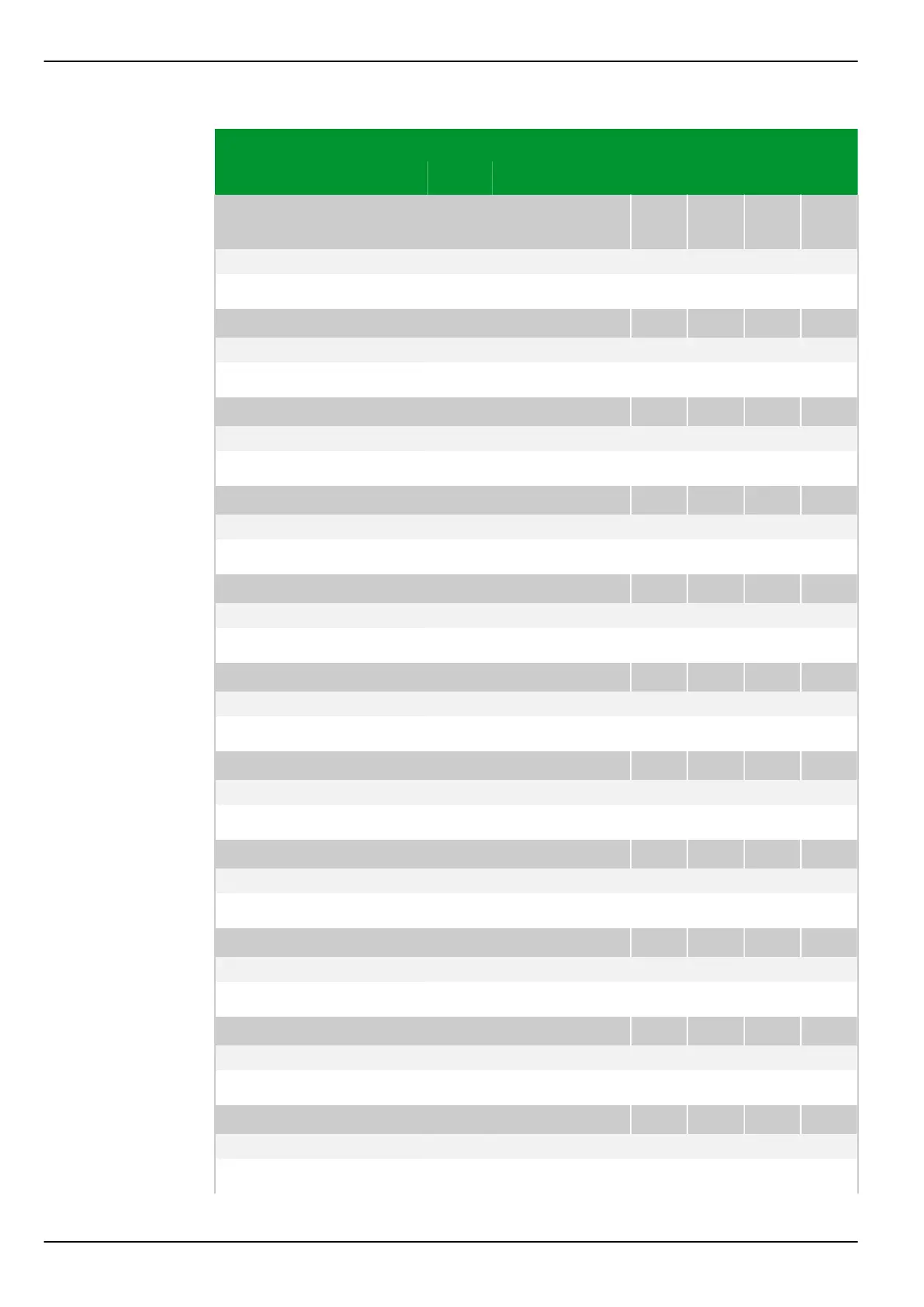

Parameter Address

Default Min Max Unit Logic Diagram

Time-voltage protec‐

tion

V<>: Enable PSx

076 000 077 000 078 000 079 000

0: No Fig. 3-134, (p. 3-182)

[spacer]

This setting defines the setting group in which V<> protection is enabled.

[spacer]

V<>: V> PSx

076 003 077 003 078 003 079 003

1.10 0.20 1.50 Vnom Fig. 3-135, (p. 3-183)

[spacer]

Setting for operate value V>.

[spacer]

V<>: V>> PSx

076 004 077 004 078 004 079 004

1.10 0.20 1.50 Vnom Fig. 3-135, (p. 3-183)

[spacer]

Setting for operate value V>>.

[spacer]

V<>: tV> PSx

076 005 077 005 078 005 079 005

1.00 0.00 100.00 s Fig. 3-135, (p. 3-183)

[spacer]

Setting for the operate delay of overvoltage stage V>.

[spacer]

V<>: tV>> PSx

076 006 077 006 078 006 079 006

1.00 0.00 100.00 s Fig. 3-135, (p. 3-183)

[spacer]

Setting for the operate delay of overvoltage stage V>>.

[spacer]

V<>: V< PSx

076 007 077 007 078 007 079 007

0.80 0.20 1.50 Vnom Fig. 3-136, (p. 3-184)

[spacer]

Setting for operate value V<.

[spacer]

V<>: V<< PSx

076 008 077 008 078 008 079 008

0.80 0.20 1.50 Vnom Fig. 3-136, (p. 3-184)

[spacer]

Setting for operate value V<<.

[spacer]

V<>: Vmin> PSx

076 046 077 046 078 046 079 046

0.25 0.00 0.60 Vnom Fig. 3-136, (p. 3-184)

[spacer]

Setting for the operate value Vmin>.

[spacer]

V<>: tV< PSx

076 009 077 009 078 009 079 009

1.00 0.00 100.00 s Fig. 3-136, (p. 3-184)

[spacer]

Setting for the operate delay of undervoltage stage V<.

[spacer]

V<>: tV<< PSx

076 010 077 010 078 010 079 010

1.00 0.00 100.00 s Fig. 3-136, (p. 3-184)

[spacer]

Setting for the operate delay of undervoltage stage V<<.

[spacer]

V<>: tTransient PSx

076 029 077 029 078 029 079 029

1.00 0.00 100.00 s Fig. 3-136, (p. 3-184)

[spacer]

Setting for the time limit of the signals generated by the undervoltage stages.

P634 7 Settings

7-176 P634/EN M/R-42-A // P634‑311‑653

Loading...

Loading...