Clocks and Power Control

MOTOROLA

MPC823e REFERENCE MANUAL

5-9

CLOCKS AND POWER

5

CONTROL

LPM—Low-Power Modes

This bit, in conjunction with the TEXPS and CSRC bits, specifies the operating mode of the

core. There are seven possible modes. In the normal mode, you can write a non-zero value

to this field. In the other modes, only a reset or interrupt (that is not from the interrupt

controller) can clear this field.

00 = Normal high/normal low mode.

01 = Doze high/doze low mode.

10 = Sleep mode.

11 = Deep sleep/power-down mode.

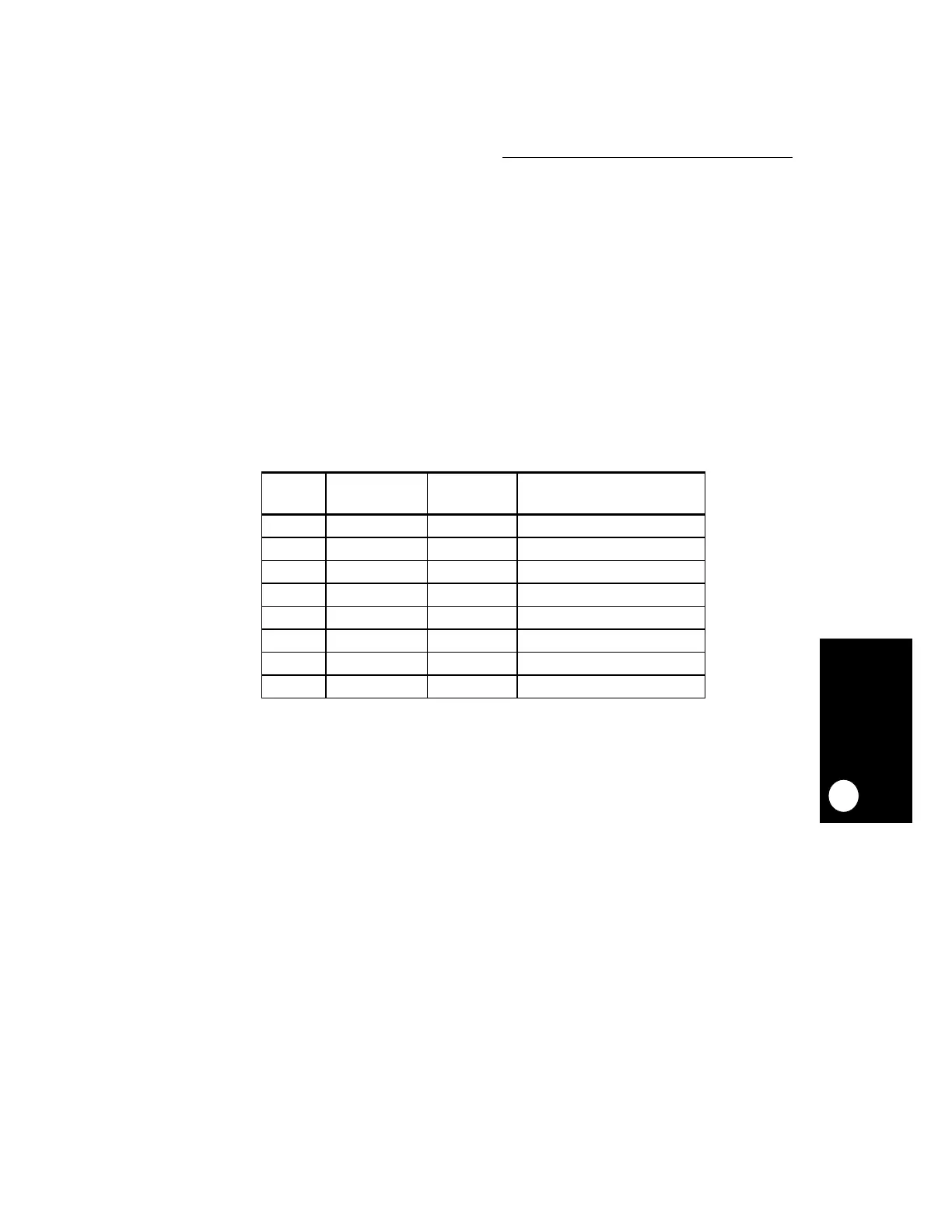

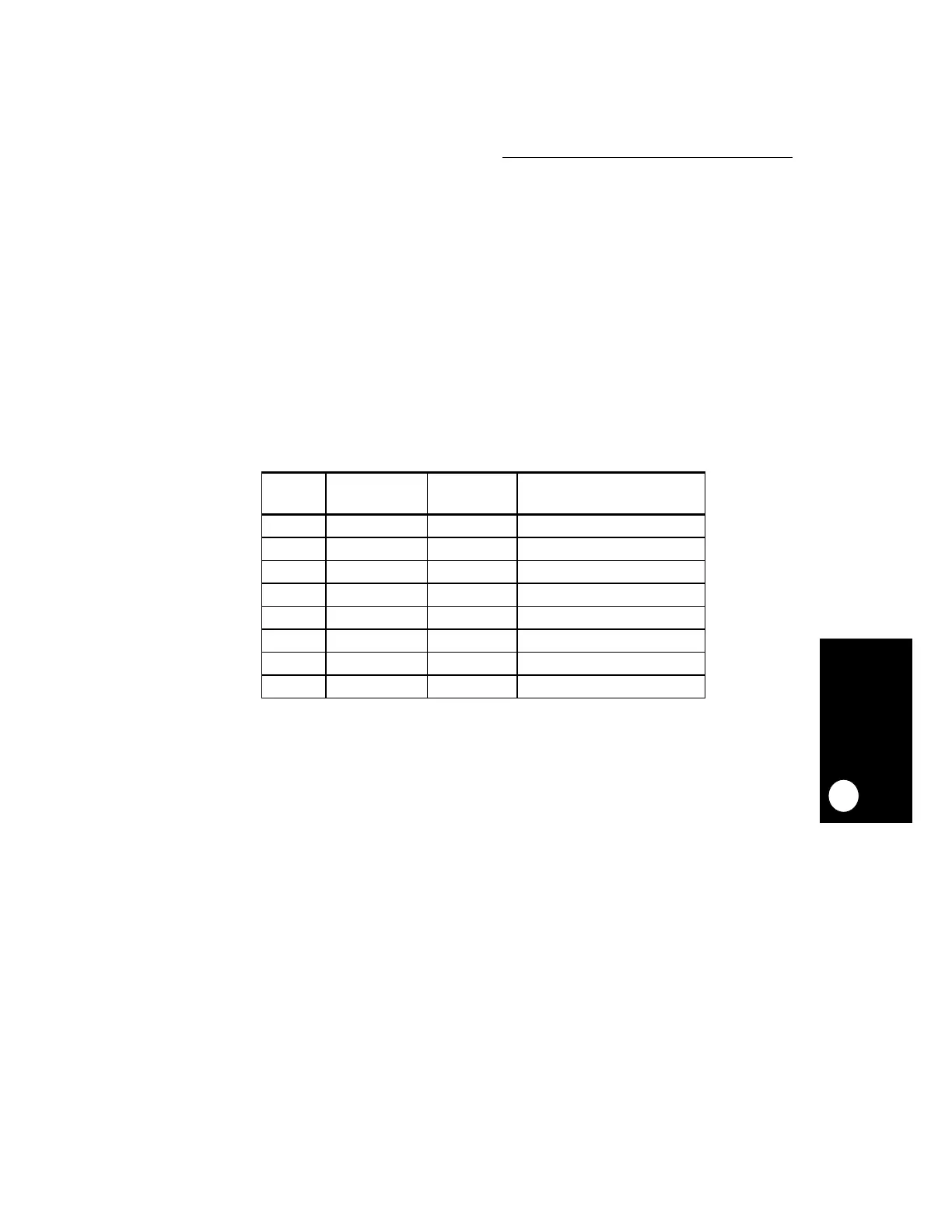

CSR—Checkstop Reset Enable

This bit enables an automatic reset when the processor enters checkstop mode. If the

processor enters debug mode at reset, then reset is not generated automatically. Refer to

Section 20.6.3.2 Debug Enable Register

for more information.

LOLRE—Loss-of-Lock Reset Enable

This bit enables hard reset generation when a loss-of-lock indication occurs, but not as a

result of altering the MF field or the processor entering deep-sleep or power-down mode.

0 = A hard reset is not generated when a loss-of-lock is indicated.

1 = A hard reset is generated when a loss-of-lock is indicated.

FIOPD—Force I/O Pull Down

This bit indicates when the address and data external pins are driven by an internal

pull-down device in sleep and deep-sleep mode.

0 = No pull-down on the address and data bus.

1 = Address and data bus is driven low in sleep and deep-sleep mode.

CSR BIT CHSTPE BIT

IN DER

CHECKSTOP

MODE

RESULT

0 0 No —

0 0 Yes —

0 1 No —

0 1 Yes Enter debug mode

1 0 No —

1 0 Yes Automatic reset

1 1 No —

1 1 Yes Enter debug mode

Loading...

Loading...