Development Capabilities and Interface

20-34 MPC823e REFERENCE MANUAL MOTOROLA

DEVELOPMENT

20

CAPABILITIES & INTERFACE

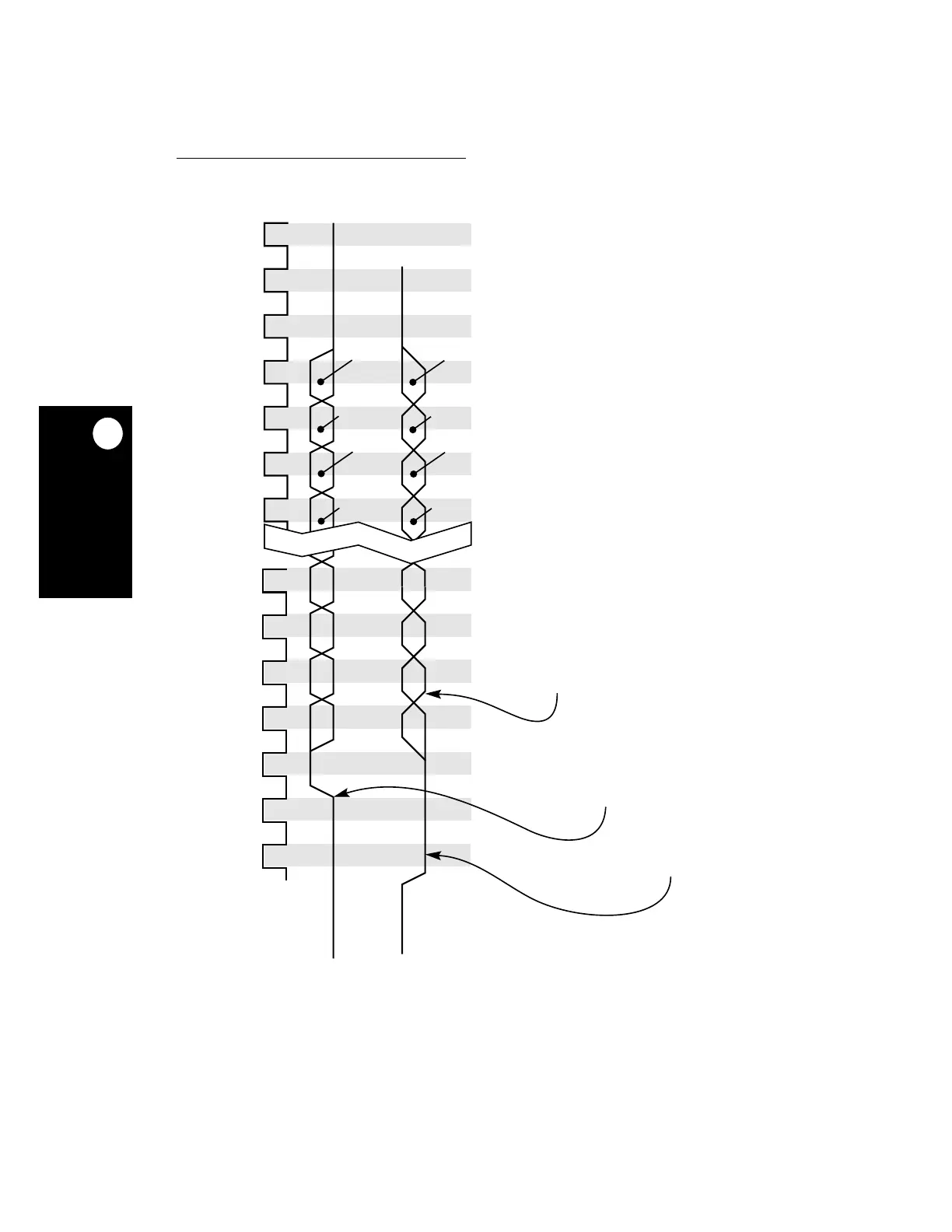

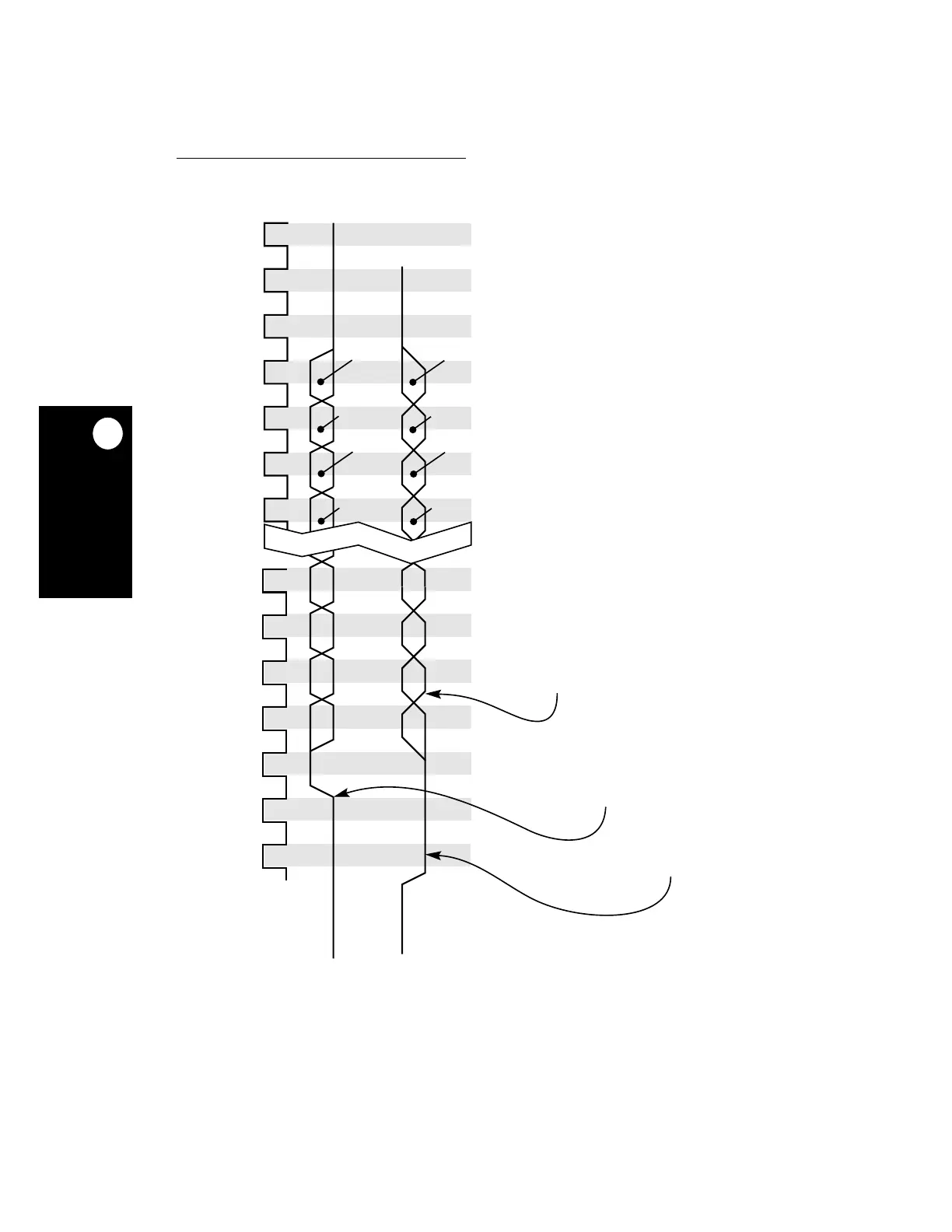

Figure 20-10. Synchronous Self-Clocked Serial Communications Timing Diagram

CLKOUT

DEBUG PORT DRIVES THE “READY” BIT ONTO DSDO WHEN THE CPU STARTS A READ OF DPIR OR DPDR.

DSDI

MODE CNTRL DI<0>START

DI<1>

S<0> S<1> DO<0>

READY

DSDO

DO<1>

DO<N>

DO<N-1>

DO<N-2>

DO<N-3>

DI<N>

DI<N-1>

DI<N-2>

DI<N-3>

DEBUG PORT DETECTS THE “START” BIT ON DSDI AND FOLLOWS THE “READY”

BIT WITH TWO STATUS BITS AND 7 OR 32 OUTPUT DATA BITS.

DEVELOPMENT TOOL DRIVES THE “START’ BIT ONTO DSDI (AFTER DETECTING THE “READY” BIT ON

DSDO WHEN IN DEBUG MODE). THE “START” BIT IS IMMEDIATELY FOLLOWED BY A MODE BIT

AND A CONTROL BIT AND THEN 7 OR 32 INPUT DATA BITS.

Loading...

Loading...