Communication Processor Module

16-88 MPC823e REFERENCE MANUAL MOTOROLA

SDMA

COMMUNICATION

16

PROCESSOR MODULE

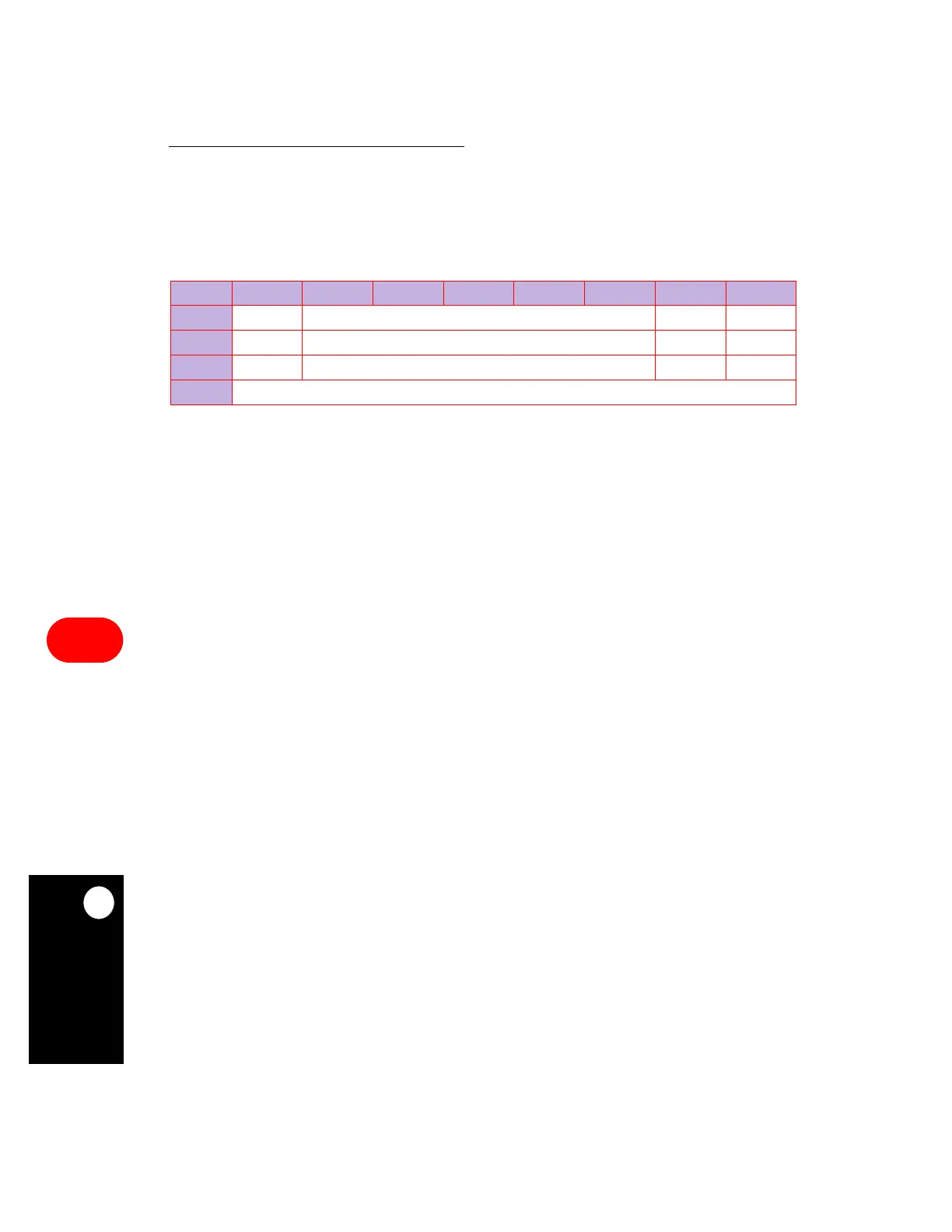

16.5.2.3 SDMA MASK REGISTER. The 8-bit read/write SDMA mask register (SDMR) has

the same bit format as the SDMA status register. If a bit in the SDMA mask register is a 1,

the corresponding interrupt in the event register is enabled. If the bit is zero, the

corresponding interrupt is masked.

SBER—SDMA Channel Bus Error Mask (SDMA function)

0 = Disable the SDMA channel bus error interrupt.

1 = Enable the SDMA channel bus error interrupt.

Bits 1–5—Reserved

These bits are reserved and must be set to 0.

DSP2—DSP Chain 2 Transmitter Interrupt Mask (DSP function)

0 = Disable the DSP chain 2 transmitter interrupt, as described in

Section 16.3.3.3 DSP Event Register.

1 = Enable the DSP chain 2 transmitter interrupt.

DSP1—DSP Chain 1 Receiver Interrupt Mask (DSP function)

0 = Disable the DSP chain 1 receiver interrupt, as described in Section 16.3.3.3 DSP

Event Register.

1 = Enable the DSP chain 1 receiver interrupt.

SDMR

BIT 0 1 2 3 4 5 6 7

FIELD SBER RESERVED DSP2 DSP1

RESET 0000

R/W R/W R/W R/W R/W

ADDR (IMMR & 0xFFFF0000) + 0x90C

Loading...

Loading...