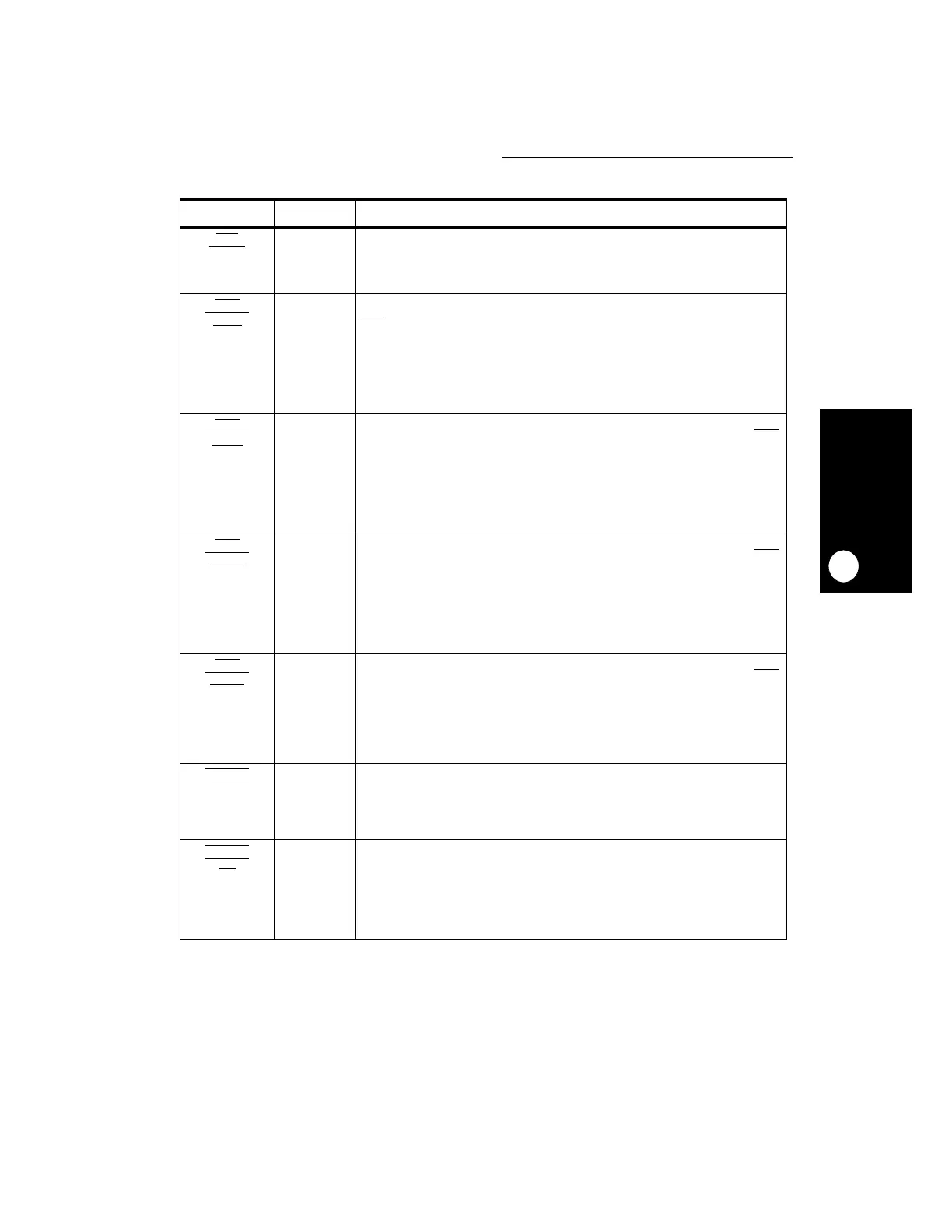

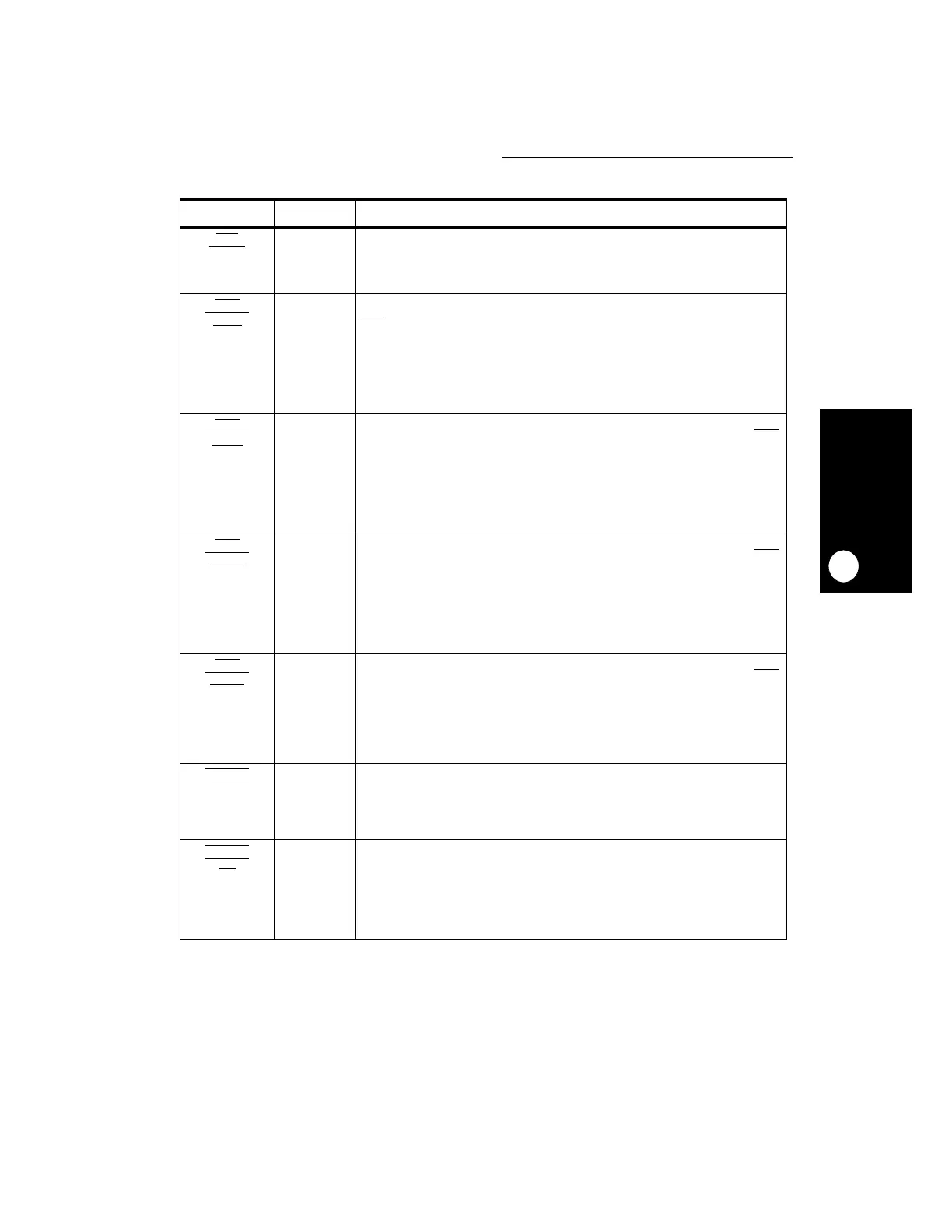

External Signals

MOTOROLA

MPC823e REFERENCE MANUAL

2-5

EXTERNAL SIGNALS

2

CS7

CE2_B

B15

Chip Select

7

—This output signal enables a peripheral or memory device at a

programmed address if defined appropriately in the BR7 and OR7 registers of the

memory controller.

Card Enable 2 Slot B

—This output signal enables odd byte transfers when

accesses to the PCMCIA Slot B are handled by the PCMCIA interface.

WE0

BS_AB0

IORD

D16

Write Enable 0

—This output signal is asserted when a write access to an external

slave controlled by the GPCM in the memory controller is initiated by the MPC823e.

WE0

is asserted if the data lane D[0:7] contains valid data to be stored by the slave

device.

Byte Select 0 on UPMA or UPMB

—This output signal is asserted as required by

the UPMA or UPMB in the memory controller whenever you program it. In a read or

write transfer, the signal is only asserted if the data lane D[0:7] contains valid data.

I/O Device Read

—This output signal is asserted when the MPC823e initiates a read

access to a region controlled by the PCMCIA interface. The signal is only asserted if

the access is to a PC Card I/O space.

WE1

BS_AB1

IOWR

E16

Write Enable 1

—This output signal is asserted when the MPC823e initiates a write

access to an external slave controlled by the GPCM in the memory controller. WE1

is asserted if the data lane D[8:15] contains valid data to be stored by the slave

device.

Byte Select 1 on UPMA or UPMB

—This output signal is asserted as required by

the UPMA or UPMB in the memory controller whenever you program it. In a read or

write transfer, the signal is only asserted if the data lane D[8:15] contains valid data.

I/O Device Write

—This output signal is asserted when the MPC823e initiates a write

access to a region controlled by the PCMCIA interface. The signal is only asserted if

the access is to a PC Card I/O space.

WE2

BS_AB2

PCOE

D15

Write Enable 2

—This output signal is asserted when the MPC823e initiates a write

access to an external slave controlled by the GPCM in the memory controller. WE2

is asserted if the data lane D[16:23] contains valid data to be stored by the slave

device.

Byte Select 2 on UPMA or UPMB

—This output signal is asserted as required by

the UPMA or UPMB in the memory controller whenever you program it. In a read or

write transfer, the signal is only asserted if the data lane D[16:23] contains valid data.

PCMCIA Output Enable

—This output signal is asserted when the MPC823e

initiates a read access to a memory region under the control of the PCMCIA

interface.

WE3

BS_AB3

PCWE

F13

Write Enable 3

—This output signal is asserted when the MPC823e initiates a write

access to an external slave controlled by the GPCM in the memory controller. WE3

is asserted if the data lane D[24:31] contains valid data to be stored by the slave

device.

Byte Select 3 on UPMA or UPMB

—This output signal is asserted as required by

the UPMA or UPMB in the memory controller whenever you program it. In a read or

write transfer, the signal is only asserted if the data lane D[24:31] contains valid data.

PCMCIA Write Enable

—This output signal is asserted when the MPC823e initiates

a write access to a memory region controlled by the PCMCIA interface.

GPL_A0

GPL_B0

E13

General-Purpose Line 0 on UPMA

—This output signal reflects the value specified

in the UPMA in the memory controller when an external transfer to a slave is

controlled by the user programmable machine A (UPMA).

General-Purpose Line 0 on UPMB

—This output signal reflects the value specified

in the UPMB in the memory controller when an external transfer to a slave is

controlled by the user programmable machine B (UPMB).

GPL_A1

GPL_B1

OE

C16

General-Purpose Line 1 on UPMA

—This output signal reflects the value specified

in the UPMA in the memory controller when an external transfer to a slave is

controlled by the user programmable machine A (UPMA).

General-Purpose Line 1 on UPMB

—This output signal reflects the value specified

in the UPMB in the memory controller when an external transfer to a slave is

controlled by the user programmable machine B (UPMB).

Output Enable

—This output signal is asserted when the MPC823e initiates a read

access to an external slave controlled by the GPCM in the memory controller.

Table 2-1. Signal Descriptions (Continued)

SIGNAL PIN NUMBER DESCRIPTION

Loading...

Loading...