Communication Processor Module

16-254 MPC823e REFERENCE MANUAL MOTOROLA

COMMUNICATION

16

SCCs

16.9.16.13 SCCx HDLC STATUS REGISTER.When a serial communication controller is

in HDLC mode, the 8-bit read-only SCCx status register is referred to as the SCCx HDLC

status register (SCCS–HDLC). Since each protocol has specific requirements, the SCCS

bits are different for each implementation. This register allows you to monitor real-time

status conditions on the RXDx pin. The real-time status of the CTSx

and CDx pins are part

of the port C parallel I/O.

Bits 0–4—Reserved

These bits are reserved and must be set to 0.

FG—Flags

When this bit is cleared, the most recently received eight bits are examined every bit time to

see if a flag is present. FG is set as soon as an HDLC flag (0x7E) is received on the line and

once it is set, it remains set at least eight bit times and the next eight received bits are

examined. If another flag occurs, this bit stays set for at least another eight bits. Otherwise,

it is cleared and the search begins again. The line is checked after the data has been

decoded by the DPLL.

0 = HDLC flags are not being received.

1 = HDLC flags are being received.

CS—Carrier Sense (DPLL)

This bit shows the real-time carrier sense of the line as determined by the DPLL.

0 = The DPLL does not sense a carrier.

1 = The DPLL senses a carrier.

ID—Idle Status

This bit is set when the RXDx pin is a logic one for 15 or more consecutive bit times. It is

cleared after a single logic zero is received.

0 = The RXDx pin is busy.

1 = The RXDx pin is idle.

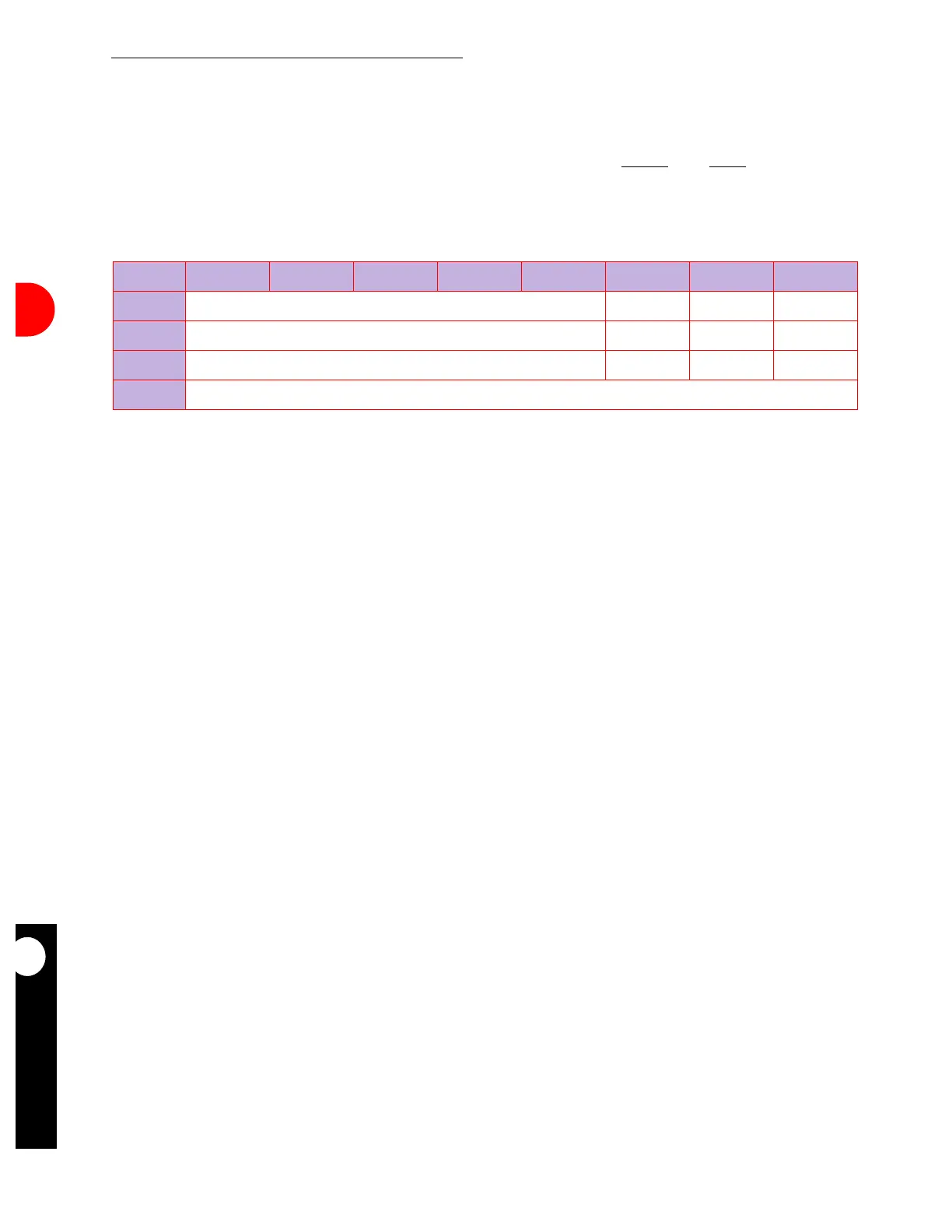

SCCS–HDLC

BIT 0 1 2 3 4 5 6 7

FIELD RESERVED FG CS ID

RESET 0 000

R/W RRORR

ADDR (IMMR & 0xFFFF0000) + 0xA37

Loading...

Loading...