xxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxx x x x xxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxx xx xx xxxxx

xxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxx xxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxx x x

xxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxx

xxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxx xxx

© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

User manual Rev. 01 — 12 January 2006 100

Philips Semiconductors

UM10161

Volume 1 Chapter 10: UART1

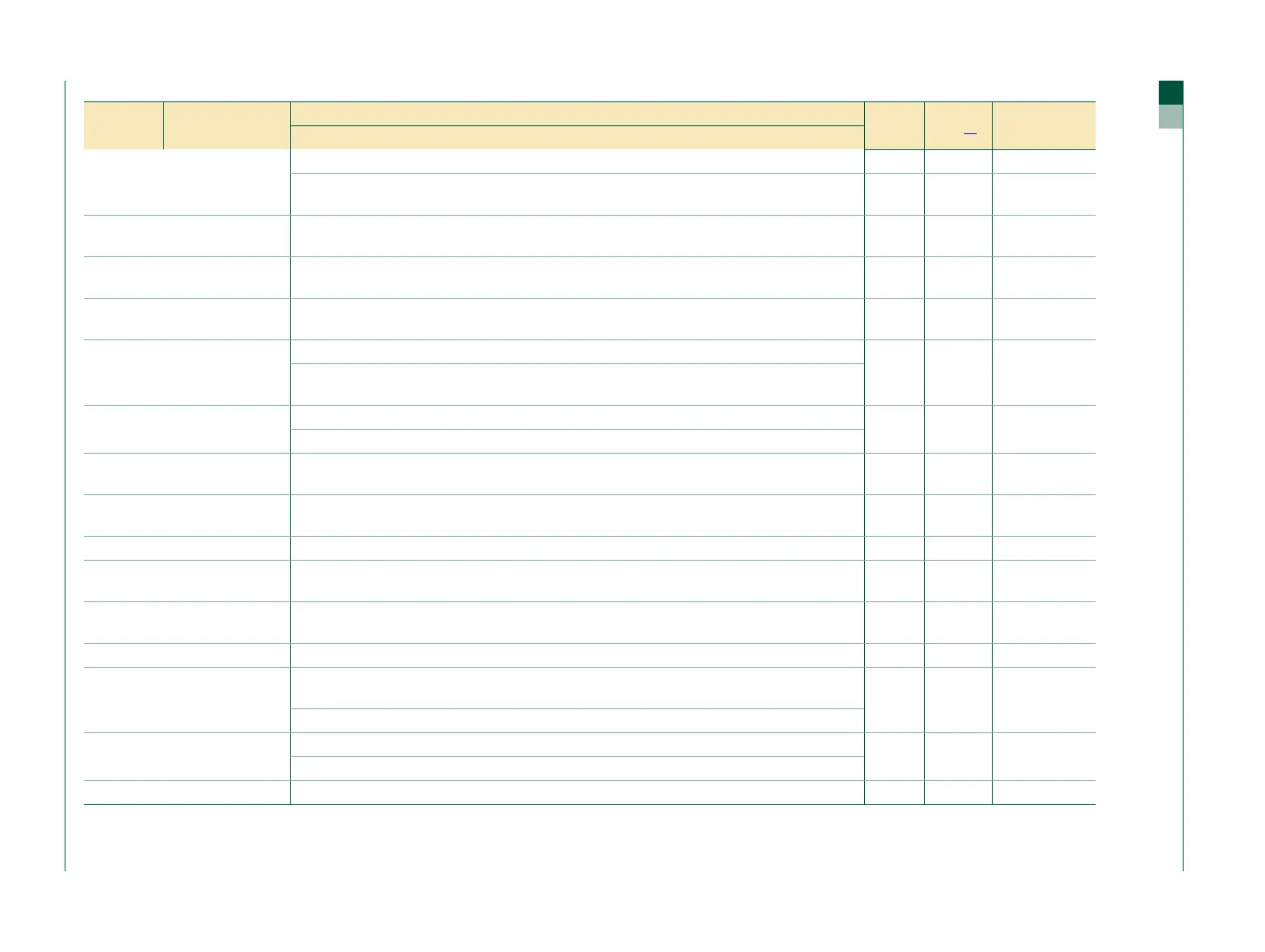

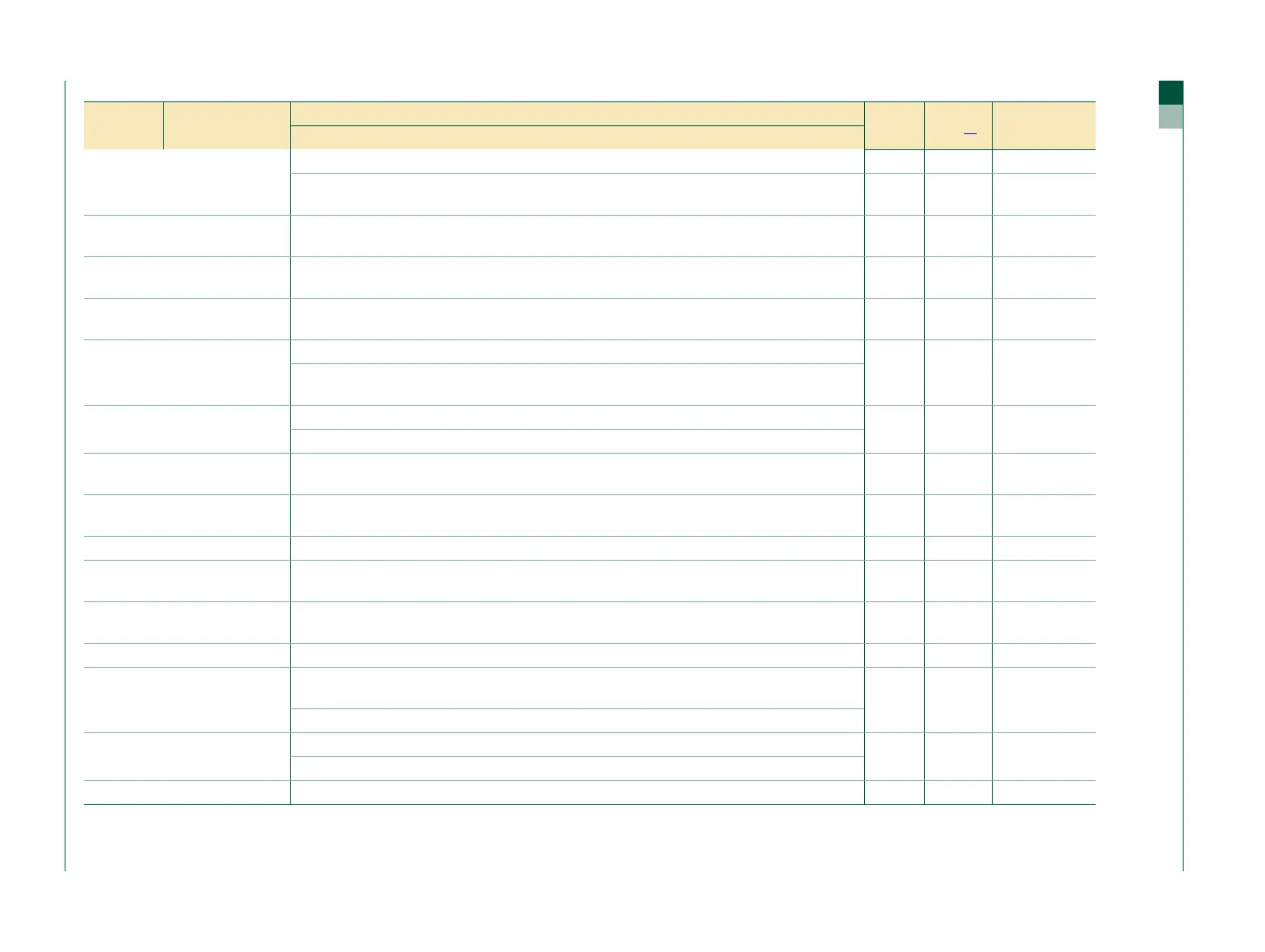

[1] Reset value reflects the data stored in used bits only. It does not include reserved bits content.

Table 98: UART1 register map

Name Description Bit functions and addresses Access Reset

value

[1]

Address

MSB LSB

BIT7 BIT6 BIT5 BIT4 BIT3 BIT2 BIT1 BIT0

U1RBR Receiver Buffer

Register

8-bit Read Data RO NA 0xE001 0000

(DLAB=0)

U1THR Transmit Holding

Register

8-bit Write Data WO NA 0xE001 0000

(DLAB=0)

U1DLL Divisor Latch LSB 8-bit Data R/W 0x01 0xE001 0000

(DLAB=1)

U1DLM Divisor Latch MSB 8-bit Data R/W 0x00 0xE001 0004

(DLAB=1)

U1IER Interrupt Enable

Register

- - - - - - En.ABTO En.ABEO R/W 0x00 0xE001 0004

(DLAB=0)

En.CTS

Int

- - - E.Modem

St.Int

En. RX

Lin.St. Int

Enable

THRE Int

En. RX

Dat.Av.Int

U1IIR Interrupt ID Reg. - - - - - - ABTO Int ABEO Int RO 0x01 0xE001 0008

FIFOs Enabled - - IIR3 IIR2 IIR1 IIR0

U1FCR FIFO Control

Register

RX Trigger - - - TX FIFO

Reset

RX FIFO

Reset

FIFO

Enable

WO 0x00 0xE001 0008

U1LCR Line Control

Register

DLAB Set

Break

Stick

Parity

Even

Par.Selct.

Parity

Enable

No. of

Stop Bits

Word Length Select R/W 0x00 0xE001 000C

U1MCR Modem Ctrl. Reg. CTSen RTSen - LoopBck. - - RTS DTR R/W 0x00 0xE001 0010

U1LSR Line Status

Register

RX FIFO

Error

TEMT THRE BI FE PE OE DR RO 0x60 0xE001 0014

U1MSR Modem Status

Register

DCD RI DSR CTS Delta

DCD

Trailing

Edge RI

Delta

DSR

Delta

CTS

RO 0x00 0xE001 0018

U1SCR Scratch Pad Reg. 8-bit Data R/W 0x00 0xE001 001C

U1ACR Auto-baud Control

Register

---- - -ABTO

IntClr

ABEO

IntClr

R/W 0x00 0xE001 0020

---- -Aut.Rstrt.ModeStart

U1FDR Fractional Divider

Register

Reserved[31:8] R/W 0x10 0xE001 0028

MulVal DivAddVal

U1TER TX. Enable Reg. TXEN - - - - - - - R/W 0x80 0xE001 0030

Loading...

Loading...