IV-11.

Interrupt

The V20 has abundant interrupt processing functions:

External interrupt

:

Interrupt by software

NMI

(

Non-maskable interrupt

)

INT

(

Maskable interrupt

)

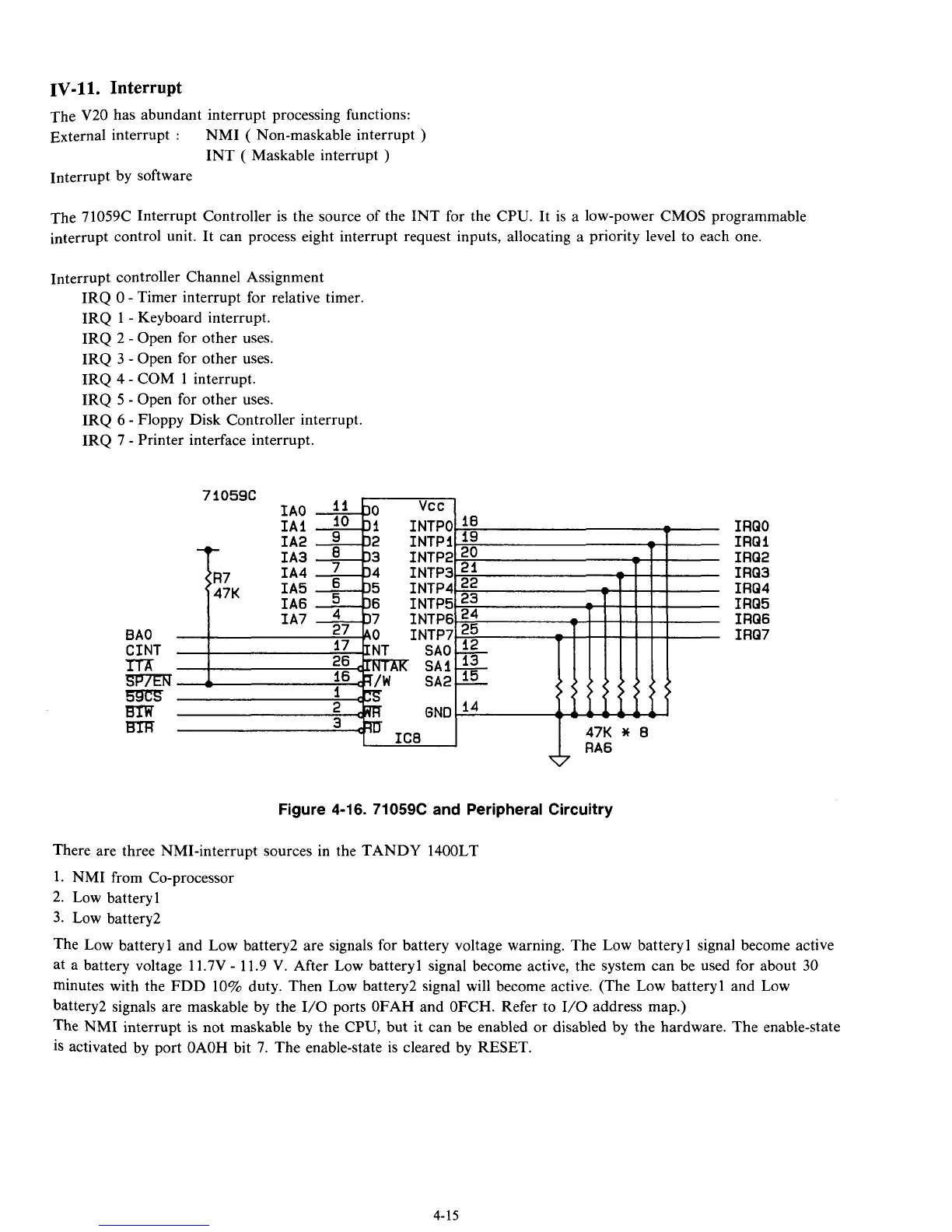

The 71059C Interrupt Controller is the source of the INT for the CPU. It is a low-power CMOS programmable

interrupt control unit. It can process eight interrupt request inputs, allocating a priority level to each one.

Interrupt controller Channel Assignment

IRQ

0

-

Timer interrupt for relative timer.

IRQ 1

-

Keyboard interrupt.

IRQ 2

-

Open for other uses.

IRQ

3

-

Open for other uses.

IRQ

4

-

COM 1 interrupt.

IRQ

5

-

Open for other uses.

IRQ

6

-

Floppy Disk Controller interrupt.

IRQ 7

-

Printer interface interrupt.

71059C

IAO

1!

h0

vcc

1

INTPC

2

INTPI

3

INTPi

4

INTP3

5

INTP4

6

INTPE

IA7

7

INTPE

BAO

CINT

m

m

Ems

B-IU

Em

:

i6

/W

SA2

GND

IC8

IRQO

IRQl

IRQ2

IRQ3

IRQ4

IRQ5

IRQ6

IRQ7

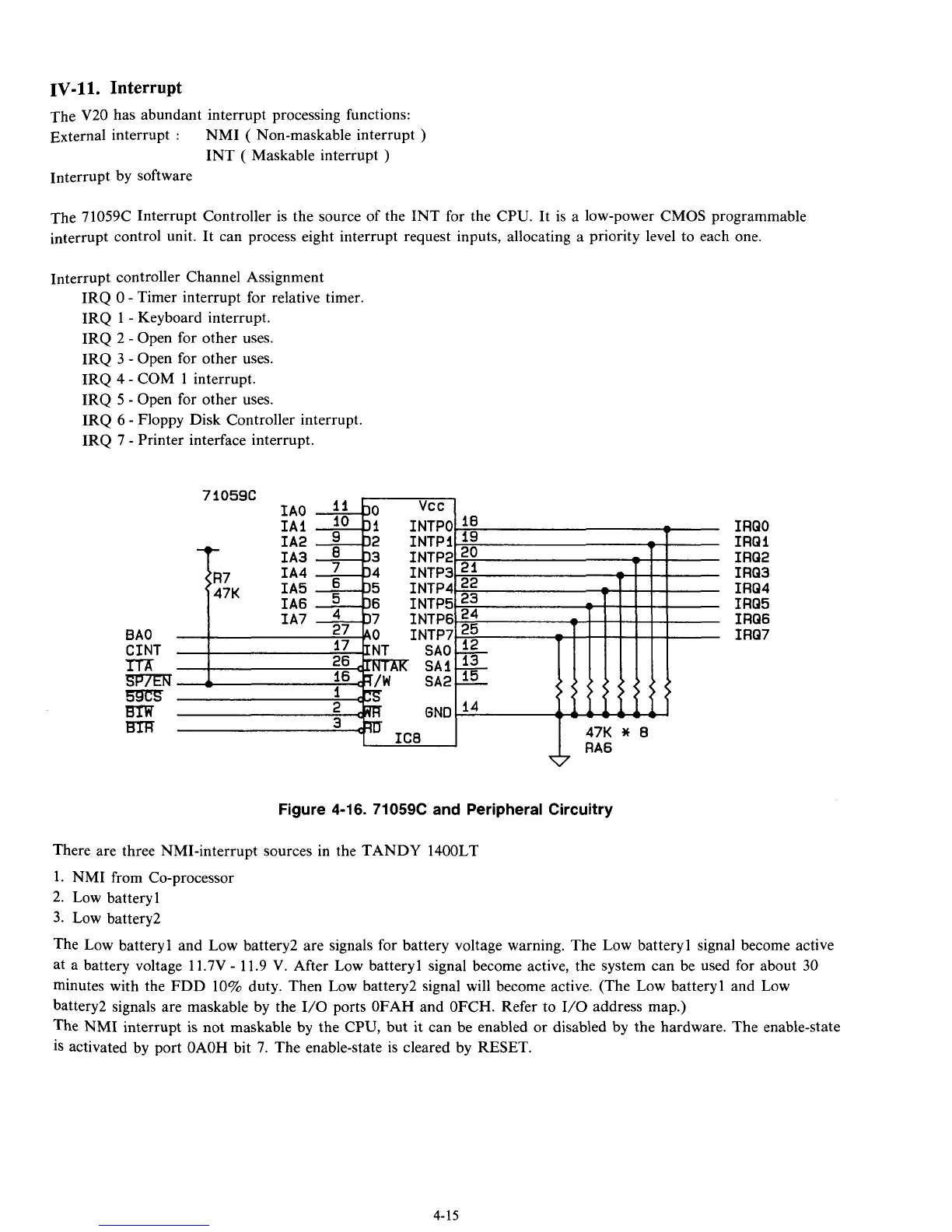

Figure 4-16. 71059C and Peripheral Circuitry

There are three NMI-interrupt sources in the TANDY 1400LT

1. NMI from Co-processor

2. Low batteryl

3.

Low battery2

The Low batteryl and Low battery2 are signals for battery voltage warning. The Low batteryl signal become active

at a battery voltage 11.7V

-

11.9 V. After Low batteryl signal become active, the system can be used for about

30

minutes with the FDD 10% duty. Then Low battery2 signal will become active. (The Low batteryl and Low

battery2 signals are maskable by the

1/0

ports OFAH and OFCH. Refer to I/O address map.)

The NMI interrupt

is

not maskable by the CPU, but it can be enabled or disabled by the hardware. The enable-state

is activated by port OAOH bit 7. The enable-state is cleared by RESET.

4-15

Loading...

Loading...