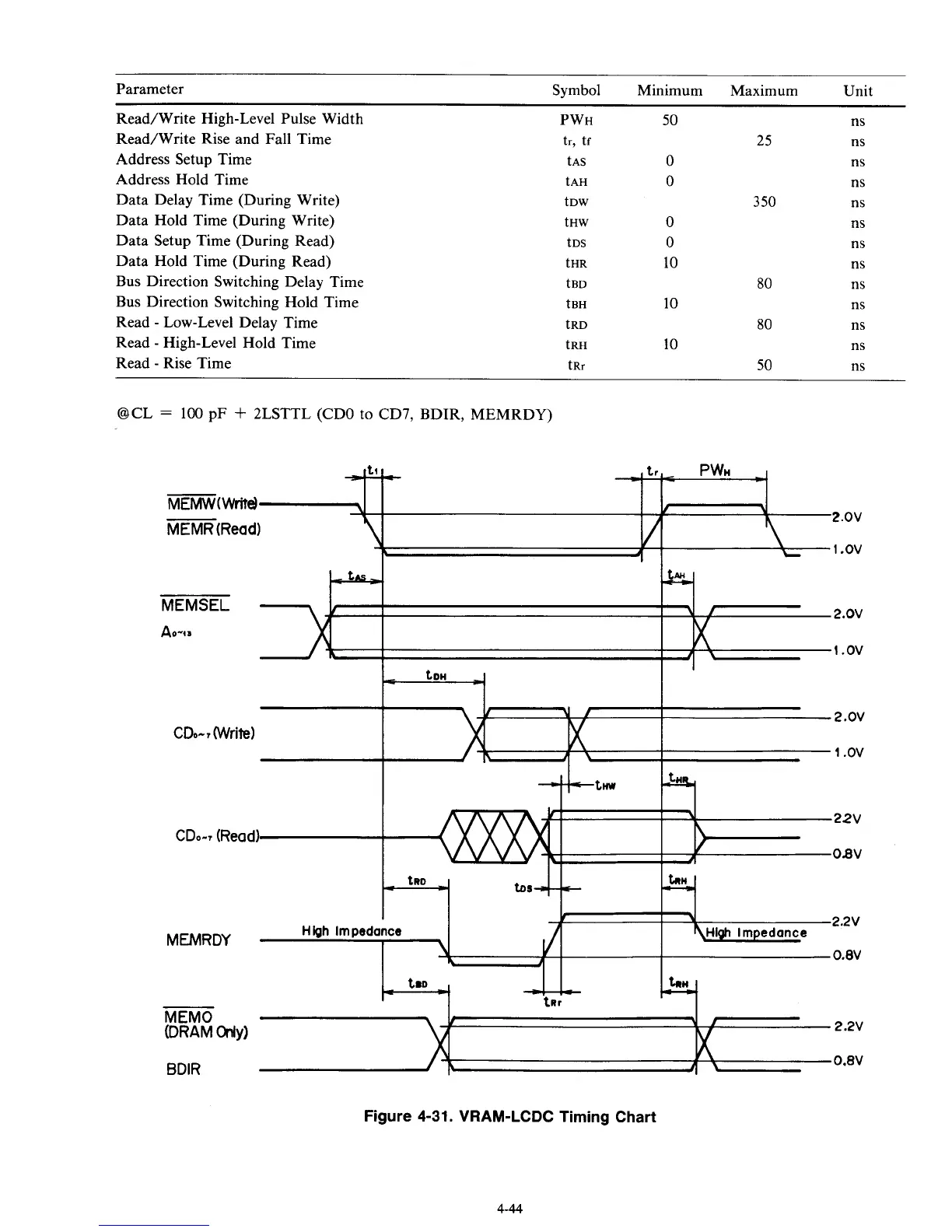

Parameter Symbol Minimum Maximum Unit

Read/Write High-Level Pulse Width

Read/Write Rise and Fall Time

Address Setup Time

Address Hold Time

Data Delay Time (During Write)

Data Hold Time (During Write)

Data Setup Time (During Read)

Data Hold Time (During Read)

Bus Direction Switching Delay Time

Bus

Direction Switching Hold Time

Read

-

Low-Level Delay Time

Read

-

High-Level Hold Time

Read

-

Rise Time

PWH

tr, tf

tAS

tAH

tDW

tHW

tDS

tHR

tBD

tBH

tRD

tRH

tRr

50

0

0

0

0

10

10

10

ns

25

ns

ns

ns

3

50

ns

ns

ns

ns

80

ns

ns

80

ns

ns

50

ns

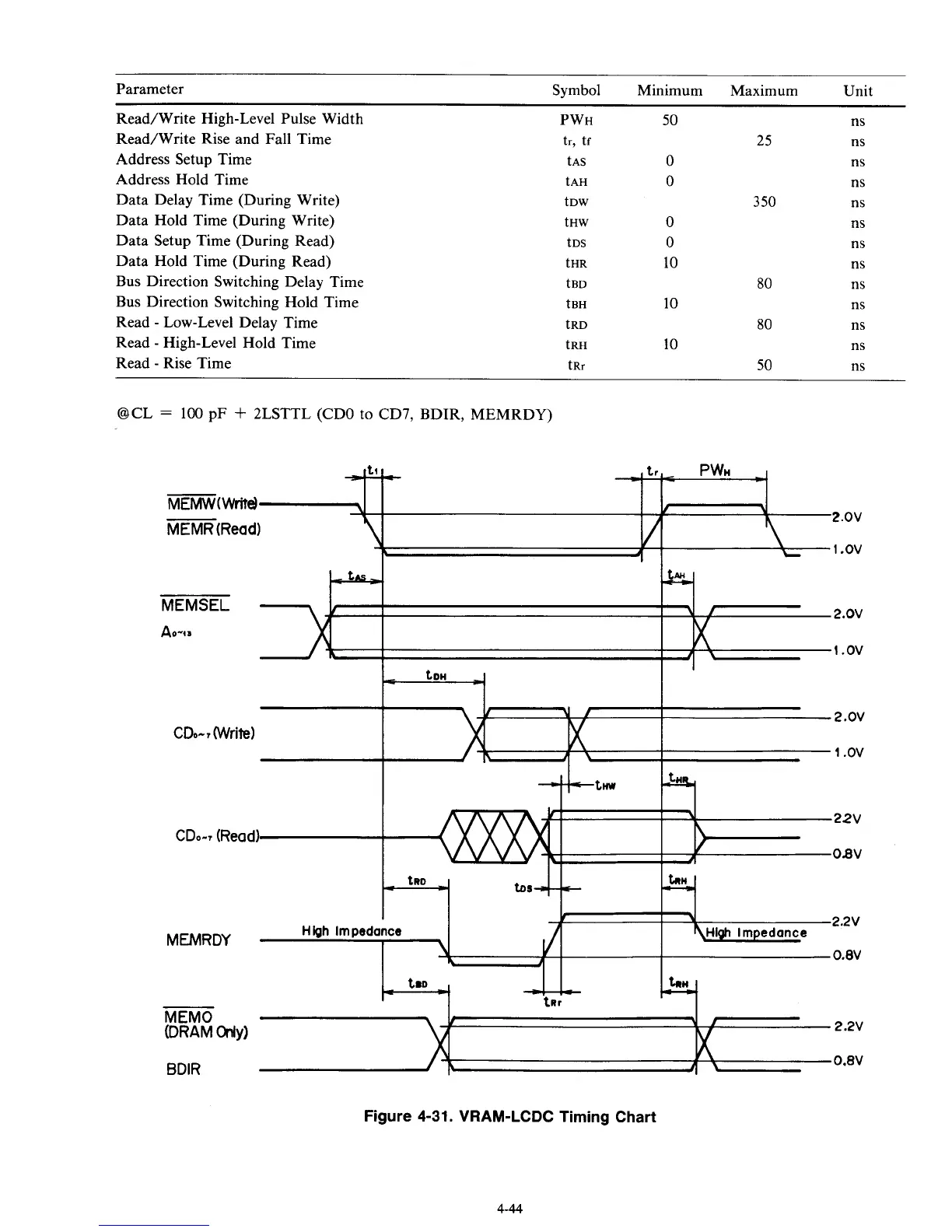

@CL

=

100

pF

4-

2LSTTL (CDO to CD7, BDIR, MEMRDY)

--

tr-

PWH

MEMW(Wd

1

\

2.0v

1

.ov

MEMR (Read)

MEMSEL

AO%

2.0v

1

.ov

2.0v

1

.ov

22v

CDo-7

(Read)

om

2.2v

0.w

MEMRDY

I

2.2v

0.8V

MEMO

(DRAM

Only)

BDIR

Figure

4-31.

VRAM-LCDC Timing Chart

4-44

Loading...

Loading...