VRAM

-

CPU Interface

The

TANDY 1400LT

uses two

8K

byte static

RAMS

(total

16K

byte) for the

VIDEO RAM.

This memory contains

640

X

200

dots data for graphic display.

The

CPU

can access it anytime without display flicker.

The

VIDEO RAM

can be accessed completely in the same way as accessing normal memory

RAM

from the

CPU.

Write and Read functions are freely executed without checking the status of the display control device.

This controller will be selected by

“0”

active

MEMSEL (VRAM

chip select signal), and

“0”

active

MEMW

(MEMORY

write signal) or

MEMR (MEMORY

read signal).

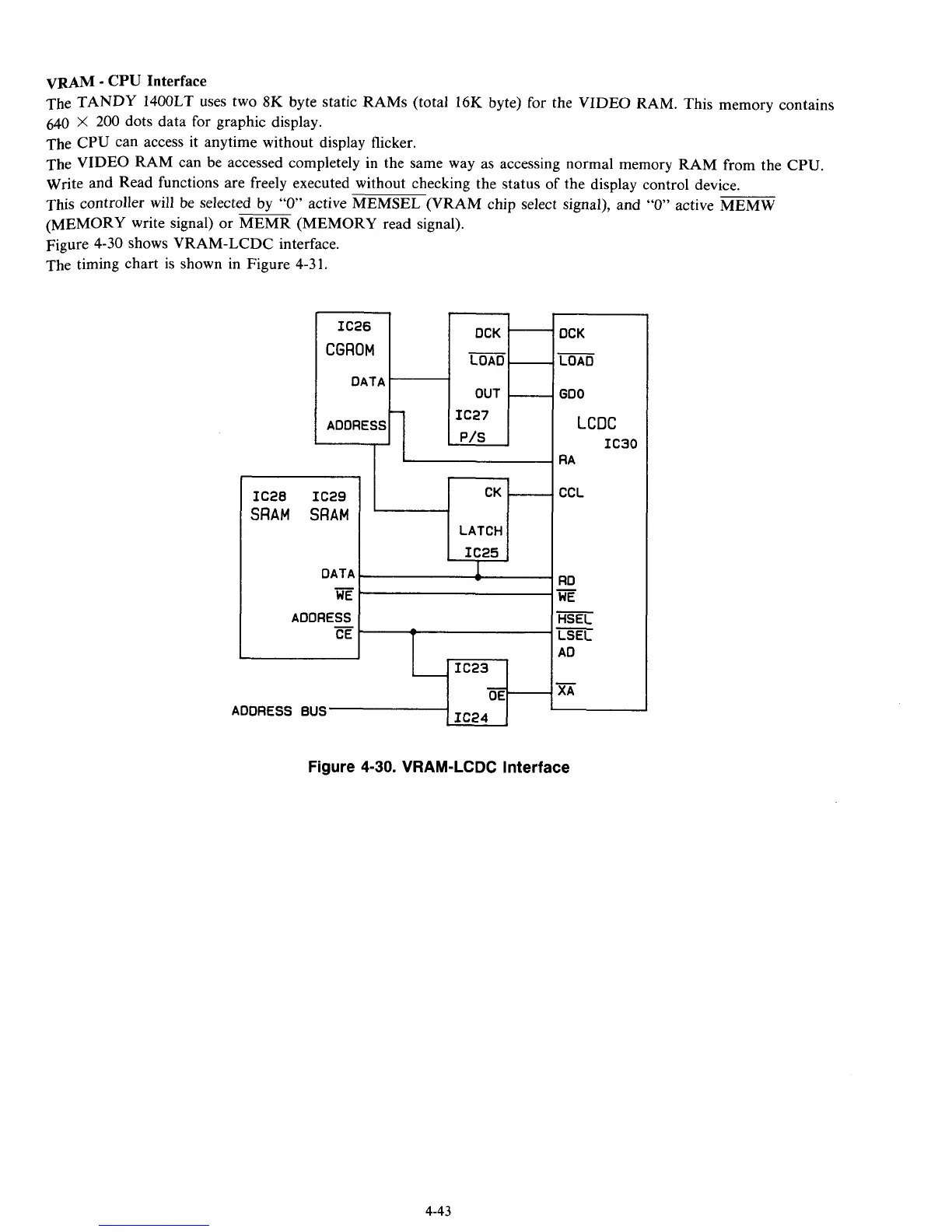

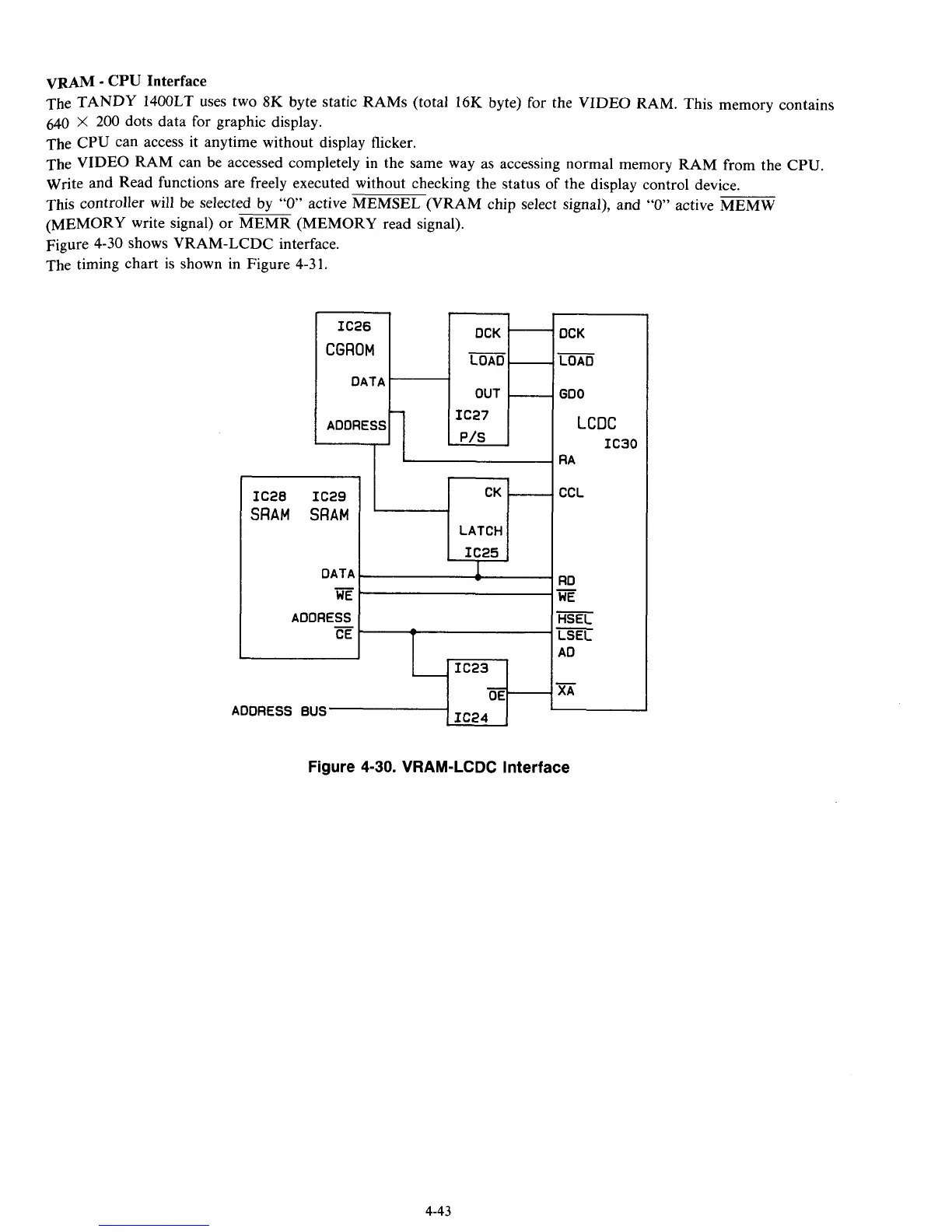

Figure

4-30

shows

VRAM-LCDC

interface.

The timing chart is shown in Figure

4-31.

IC28 IC29

SRAM

SRAM

DATA

WE

ADDRESS

CE

-

-

OCKl

CK

-

LATCH

IC25,

-

-

1

’

-

-

-I

LOAD

IC23

-

OE

-

IC24

ADDRESS

BUS

-

DCK

LOAD

GOO

-

LCDC

IC30

RA

CCL

RD

WE

HSEC

LSEC

AD

-

-

-

-

XA

Figure

4-30.

VRAM-LCDC

Interface

4-43

Loading...

Loading...