A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 239 / 812

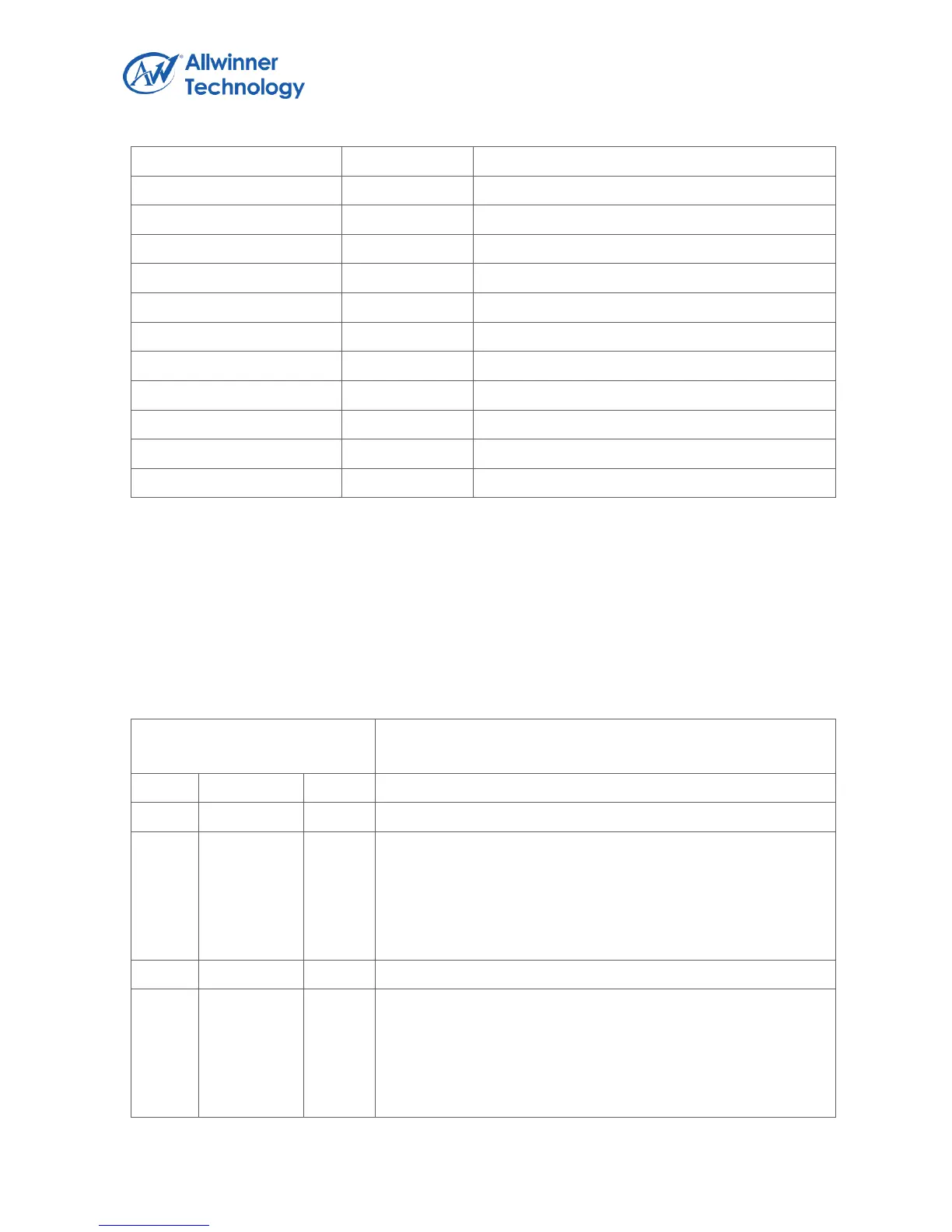

Port n Multi-Driving Register 0 (n from 0 to 8)

Port n Multi-Driving Register 1 (n from 0 to 8)

Port n Pull Register 0 (n from 0 to 8)

Port n Pull Register 1 (n from 0 to 8)

PIO Interrrupt Configure Register 0

PIO Interrrupt Configure Register 1

PIO Interrrupt Configure Register 2

PIO Interrrupt Configure Register 3

PIO Interrupt Control Register

PIO Interrupt Status Register

PIO Interrupt Debounce Register

1.19.4. Port Register Description

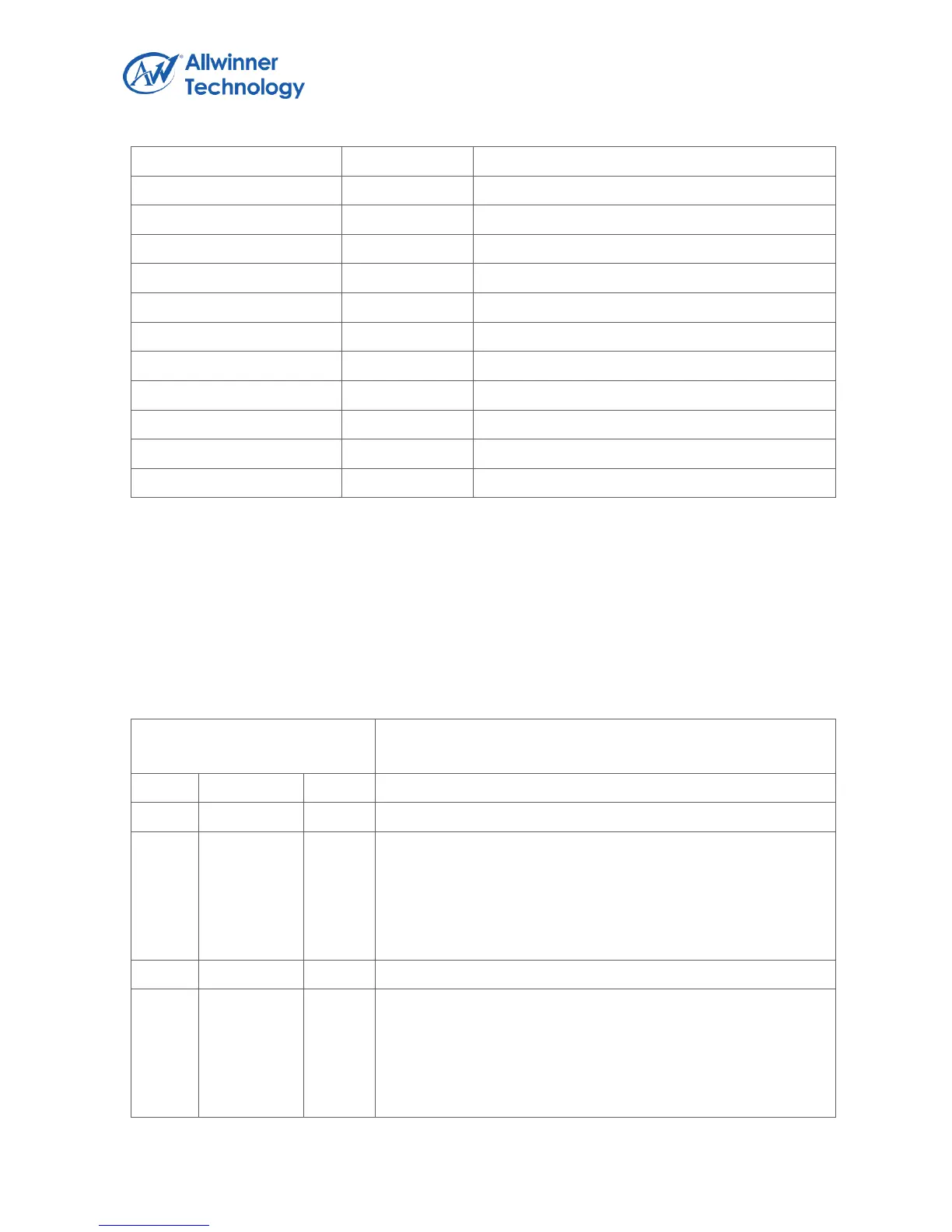

1.19.4.1. PA CONFIGURE REGISTER 0

Register Name: PA_CFG0

Default Value: 0x0000_0000

PA7_SELECT

000: Input 001: Output

010:ETXD0 011: SPI3_MOSI

100: Reserved 101: GTXD0

110: Reserved 111: Reserved

PA6_SELECT

000: Input 001: Output

010: ETXD1 011: SPI3_CLK

100: Reserved 101: GTXD1

110: Reserved 111: Reserved

Loading...

Loading...