A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 173 / 812

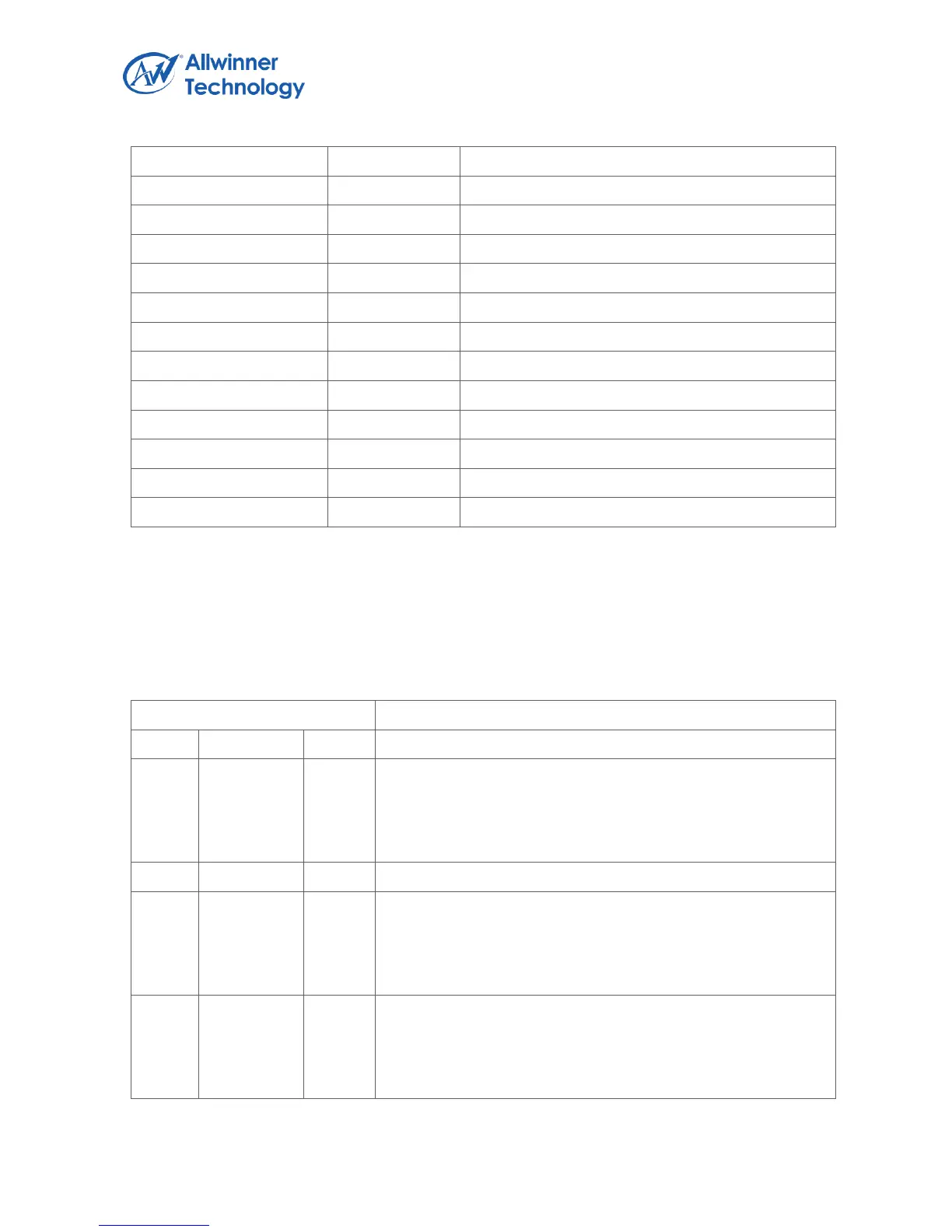

DAC Analog Control Register

DAC/ ADC Performance Tuning Register

ADC FIFO Control Register

ADC Analog Control Register

DAC TX FIFO Counter Register

ADC RX FIFO Counter Register

System Calibration Verify Register

MIC gain & Phone out Control Register

1.13.4. Audio Codec Register Description

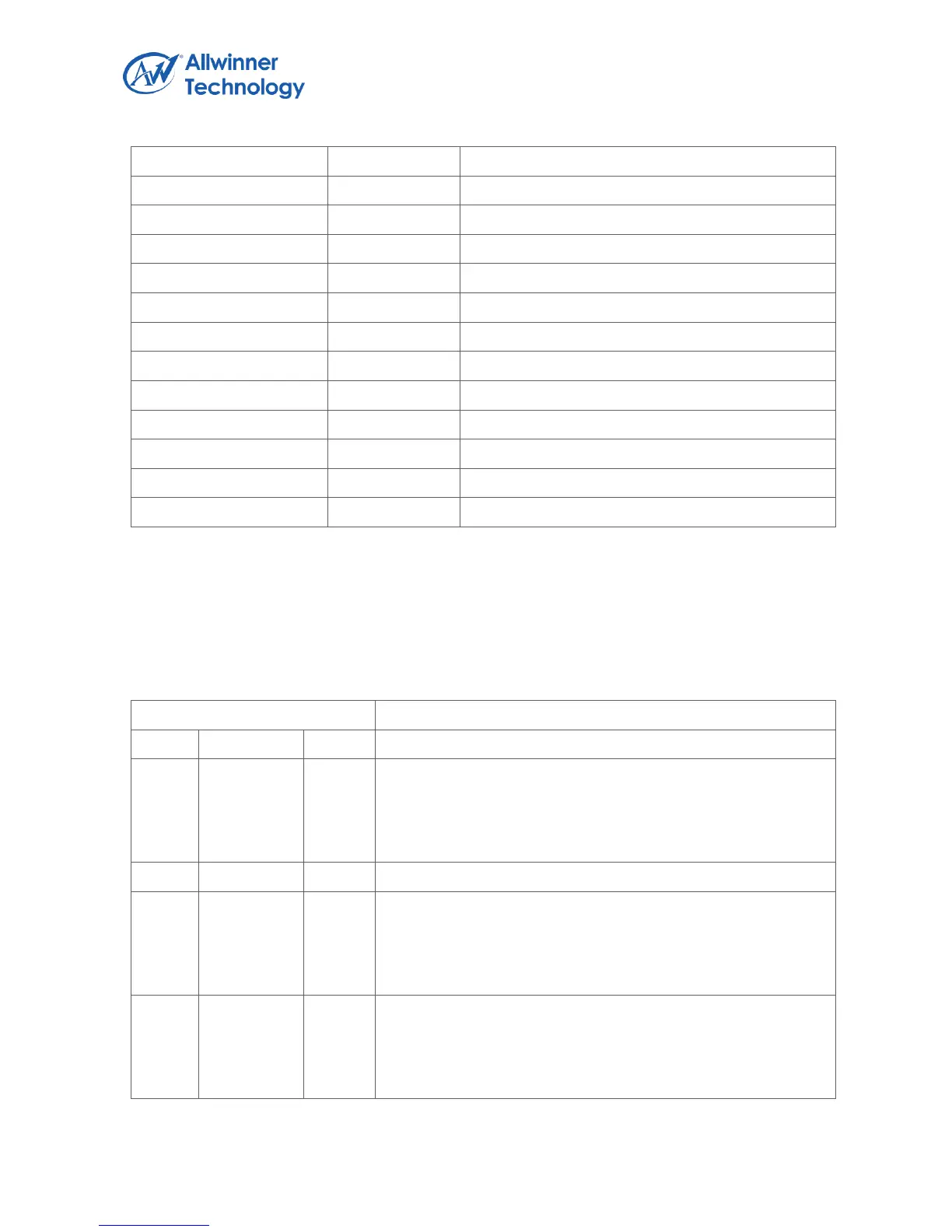

1.13.4.1. DAC DIGITAL PART CONTROL REGISTER

Register Name: AC_DAC_DPC

EN_DA.

DAC Digital Part Enable

0: Disable

1: Enable

MODQU.

Internal DAC Quantization Levels

Levels=[7*(21+MODQU[3:0])]/128

Default levels=7*21/128=1.15

DWA.

DWA Function Disable

0: Enable

1: Disable

Loading...

Loading...