A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 627 / 812

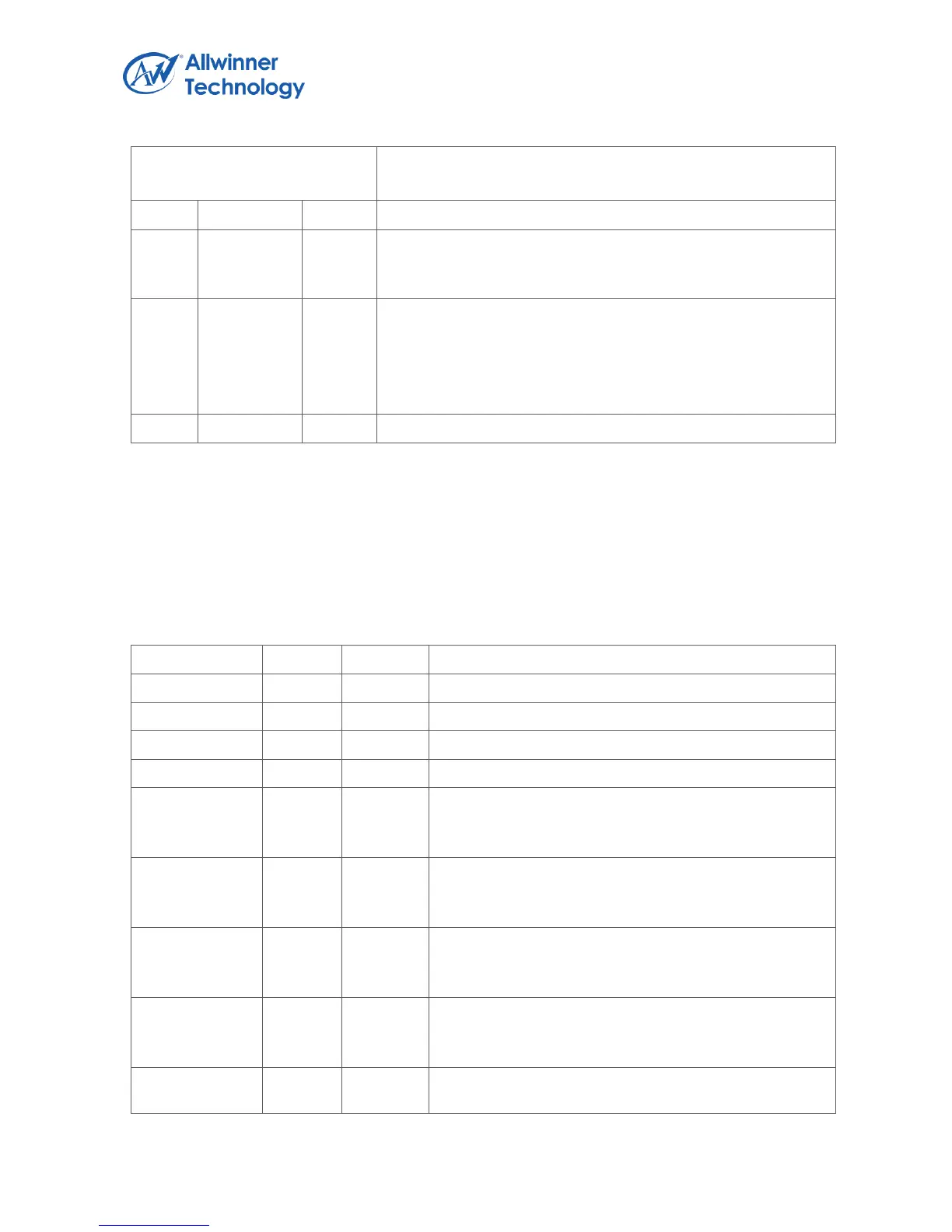

Register Name: UART_HALT

Default Value: 0x0000_0000

this bit self clear to 0 to finish update process. Write 0 to this

bit has no effect.

1: Update trigger, Self clear to 0 when finish update.

CHCFG_AT_BUSY

This is an enable bit for the user to change LCR register

configuration (except for the DLAB bit) and baudrate register

(DLH and DLL) when the UART is busy (USB[0] is 1).

1: Enable change when busy

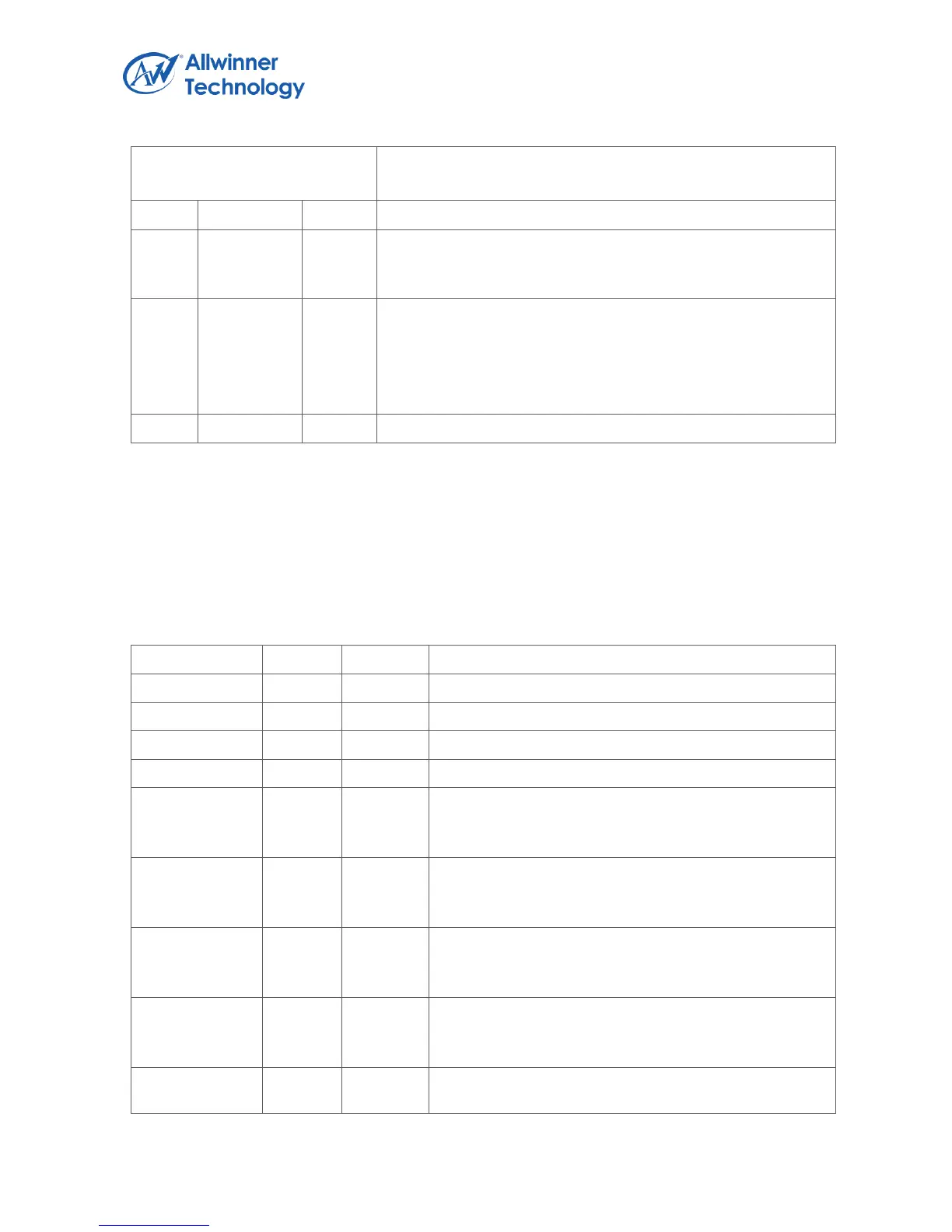

6.4.5. UART Special Requirement

6.4.5.1. UART PIN LIST

UART Request To Send

This active low output signal informs Modem that the

UART is ready to send data

UART Clear To End

This active low signal is an input showing when Modem is

ready to accept data

UART Data Terminal Ready

This active low output signal informs Modem that the

UART is ready to establish a communication link

UART Data Set Ready

This active low signal is an input indicating when Modem

is ready to set up a link with the UART0

UART Data Carrier Detect

This active low signal is an input indicating when Modem

Loading...

Loading...