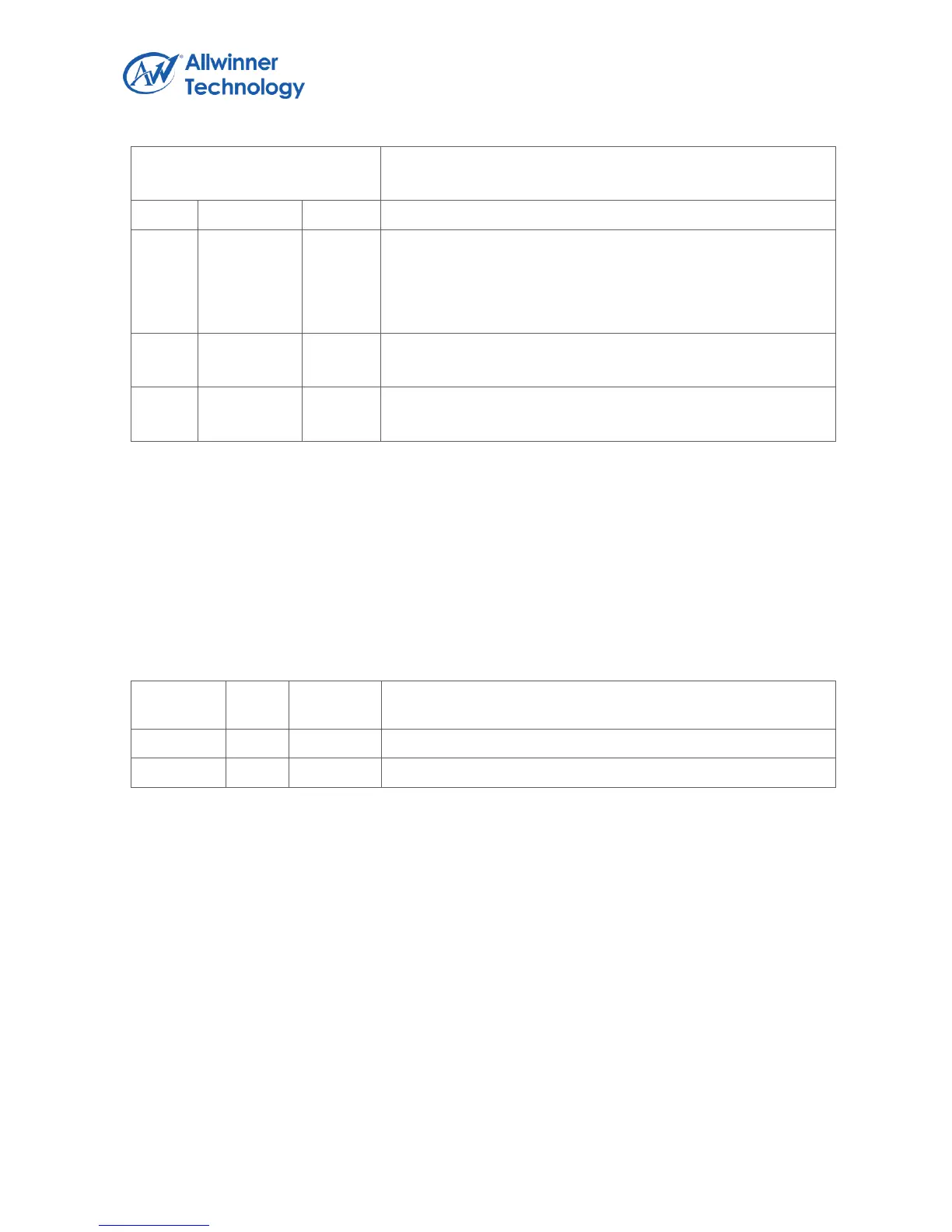

MS_PRIORITY

CPU and DVFS BUSY set priority select

0: CPU has higher priority

1: DVFS has higher priority

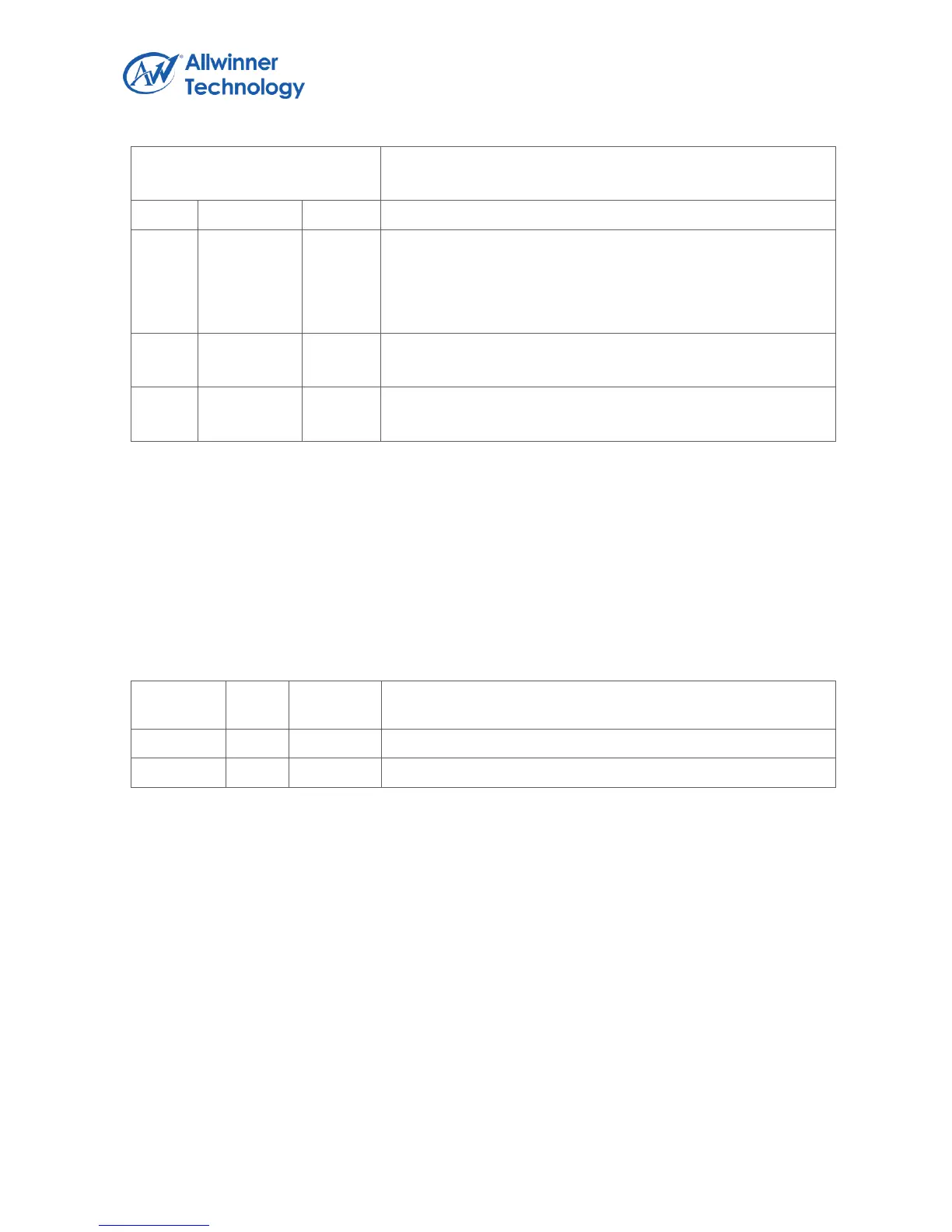

6.2.5.2. TWI CONTROLLER OPERATION

There are four operation modes on the 2-Wire bus which dictates the communications method. They

are Master Transmit, Master Receive, Slave Transmit and Slave Receive. In general, CPU host

controls TWI by writing commands and data to it’s registers. The TWI interrupts the CPU host for

the attention each time a byte transfer is done or a START/STOP conditions is detected. The CPU

host can also poll the status register for current status if the interrupt mechanism is not disabled by

the CPU host.

When the CPU host wants to start a bus transfer, it initiates a bus START to enter the master mode

by setting IM_STA bit in the 2WIRE_CNTR register to high (before it must be low). The TWI will

assert INT line and INT_FLAG to indicate a completion for the START condition and each

consequent byte transfer. At each interrupt, the micro-processor needs to check the 2WIRE_STAT

Loading...

Loading...