A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 136 / 812

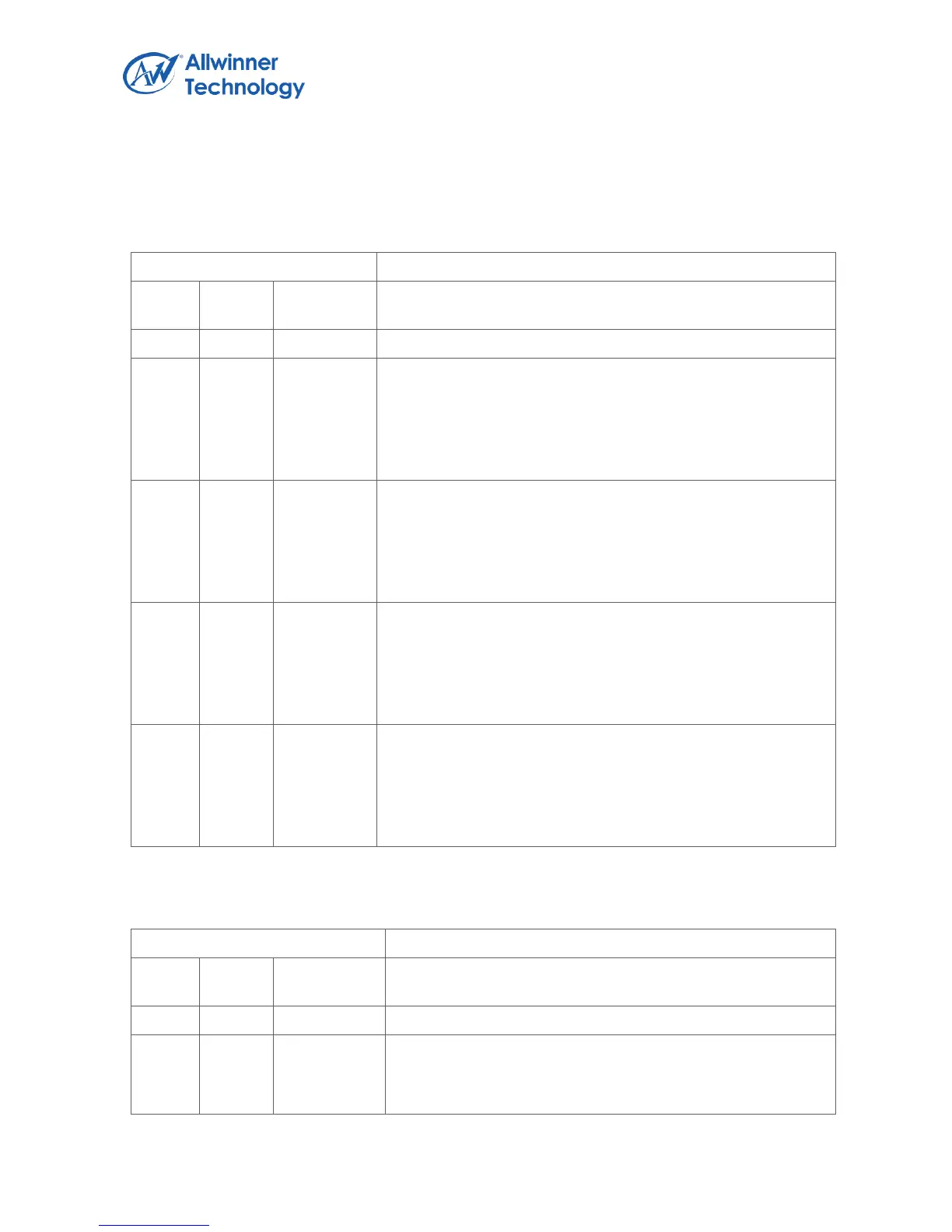

1.10.3. High Speed Timer Controller Register

1.10.3.1. HS TIMER IRQ ENABLE REGISTER (DEFAULT: 0X00000000)

Register Name: HS_TMR_IRQ_EN_REG

HS_TMR3_INT_EN.

High Speed Timer 3 Interrupt Enable.

0: No effect;

1: High Speed Timer 3 Interval Value reached interrupt

enable.

HS_TMR2_INT_EN.

High Speed Timer 2 Interrupt Enable.

0: No effect;

1: High Speed Timer 2 Interval Value reached interrupt

enable.

HS_TMR1_INT_EN.

High Speed Timer 1 Interrupt Enable.

0: No effect;

1: High Speed Timer 1 Interval Value reached interrupt

enable.

HS_TMR0_INT_EN.

High Speed Timer 0 Interrupt Enable.

0: No effect;

1: High Speed Timer 0 Interval Value reached interrupt

enable.

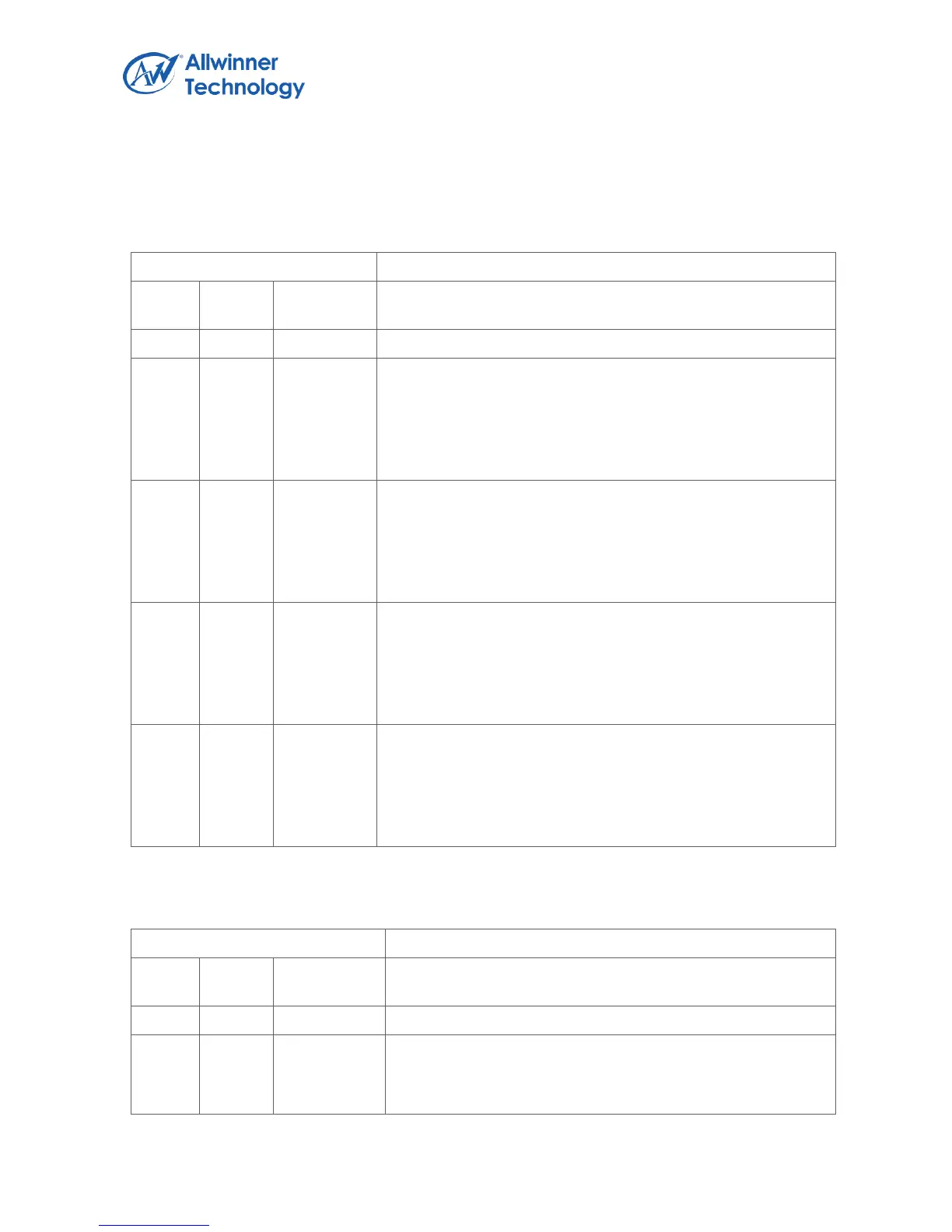

1.10.3.2. HS TIMER IRQ STATUS REGISTER (DEFAULT: 0X00000000)

Register Name: HS_TMR_IRQ_STAS_REG

HS_TMR3_IRQ_PEND.

High Speed Timer 3 IRQ Pending. Set 1 to the bit will clear it.

0: No effect;

Loading...

Loading...