A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 608 / 812

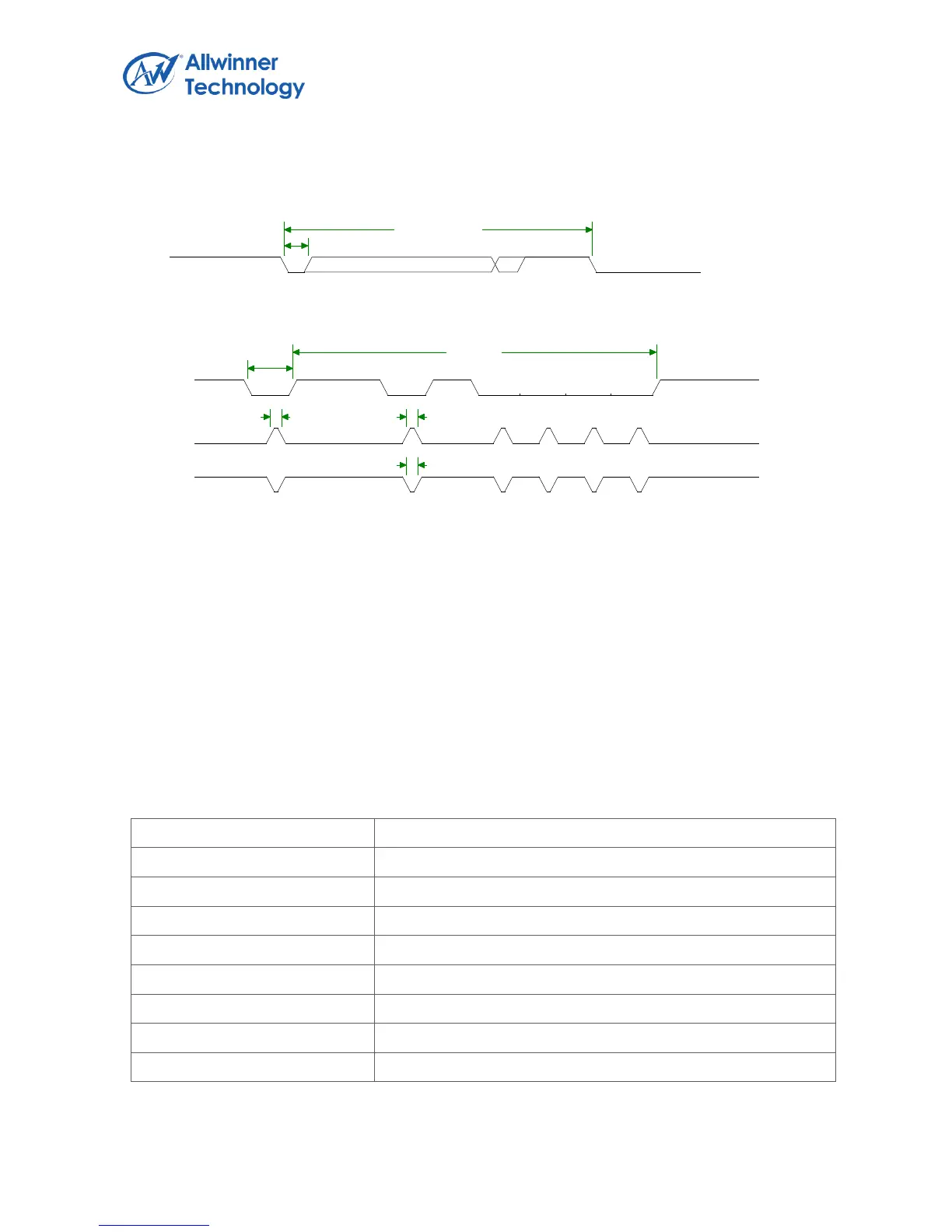

6.4.2. UART Timing Diagram

Serial IrDA Data Format

6.4.3. UART Register List

There are 8 UART controllers. UART1 has full modem control signals, including RTS, CTS, DTR, DSR,

DCD and RING signal. UART2/3 has two data flow control singals, including RTS and CTS. Other UART

controller has only two data signals, including DIN and DOUT. All UART controllers can be configured as

Serial IrDA.

Loading...

Loading...