A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 717 / 812

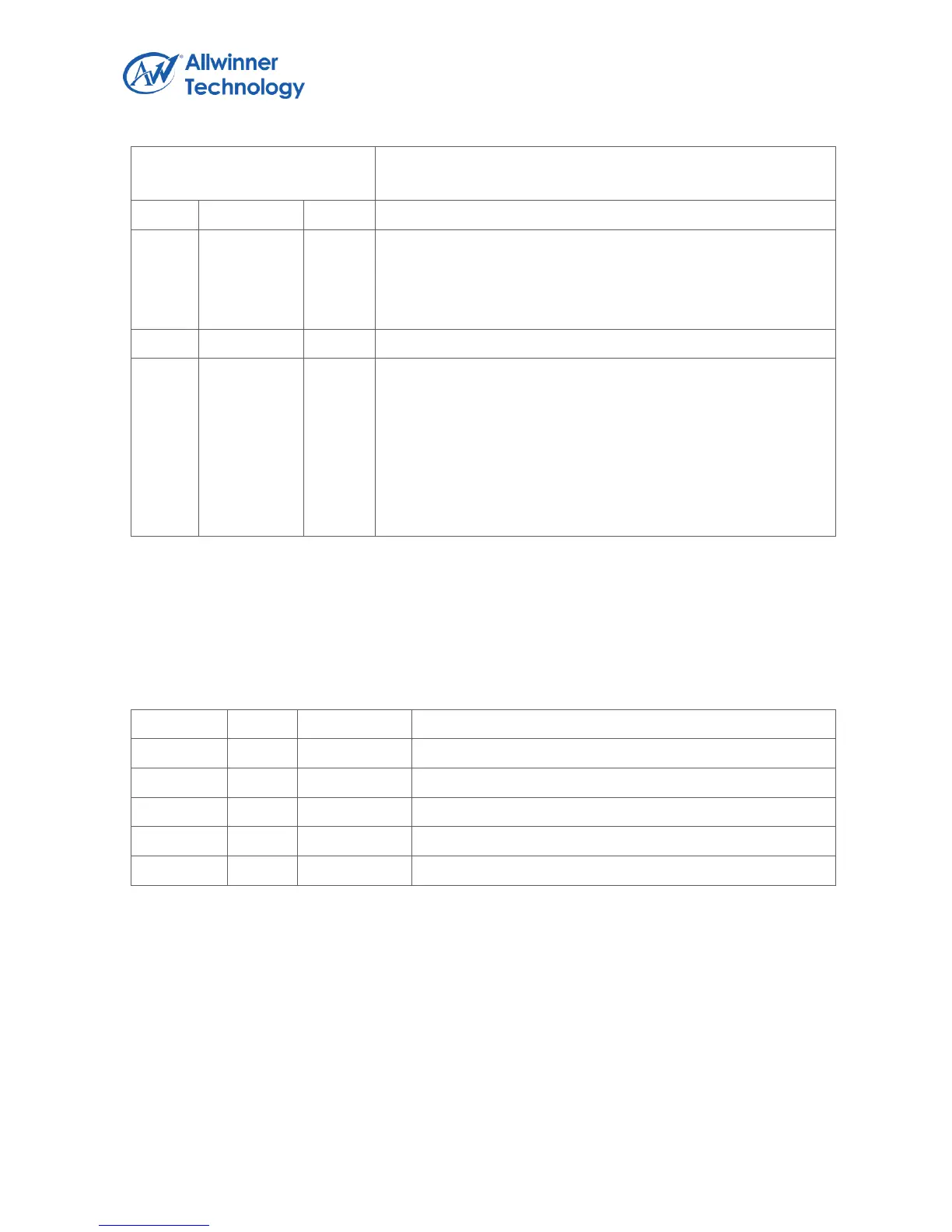

Register Name: DA_RXCHMAP

Default Value: 0x0000_3210

001: 2

nd

sample

010: 3

rd

sample

011: 4

th

sample

Others: Reserved

RX_CH0_MAP

RX Channel0 Mapping

000: 1

st

sample

001: 2

nd

sample

010: 3

rd

sample

011: 4

th

sample

Others: Reserved

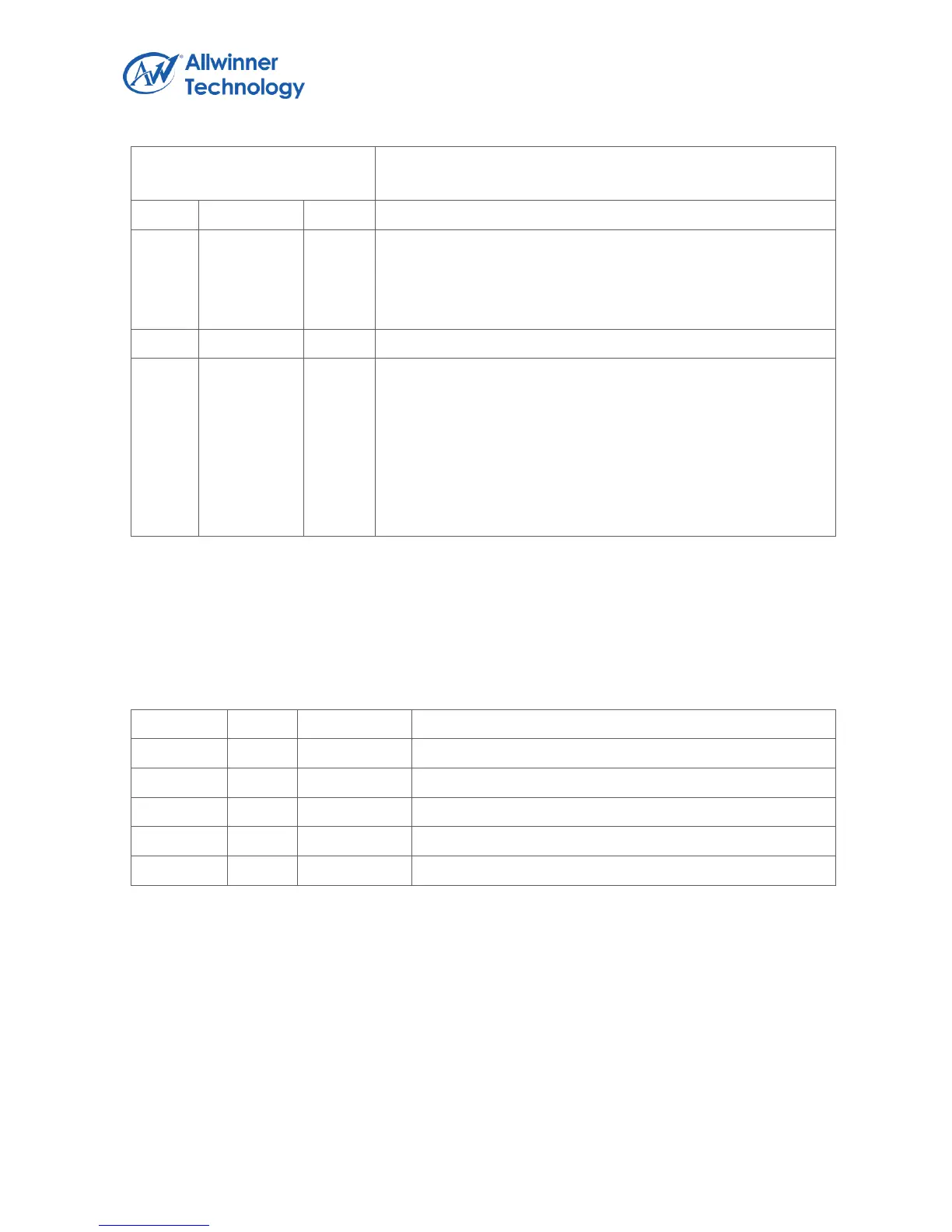

6.9.6. Digital Audio Interface Special Requirement

6.9.6.1. DIGITAL AUDIO INTERFACE PIN LIST

Digital Audio Serial Clock

Digital Audio Sample Rate Clock/ Sync

Digital Audio Serial Data Output

Digital Audio Serial Data Input

Digital Audio MCLK Output

6.9.6.2. DIGITAL AUDIO INTERFACE MCLK AND BCLK

The Digital Audio Interface can support sampling rates from 128fs to 768fs, where fs is the audio

sampling frequency typically 32kHz, 44.1kHz, 48kHz or 96kHz. For different sampling frequencies,

the tables list the coefficient value of MCLKDIV and BCLKDIV.

Loading...

Loading...