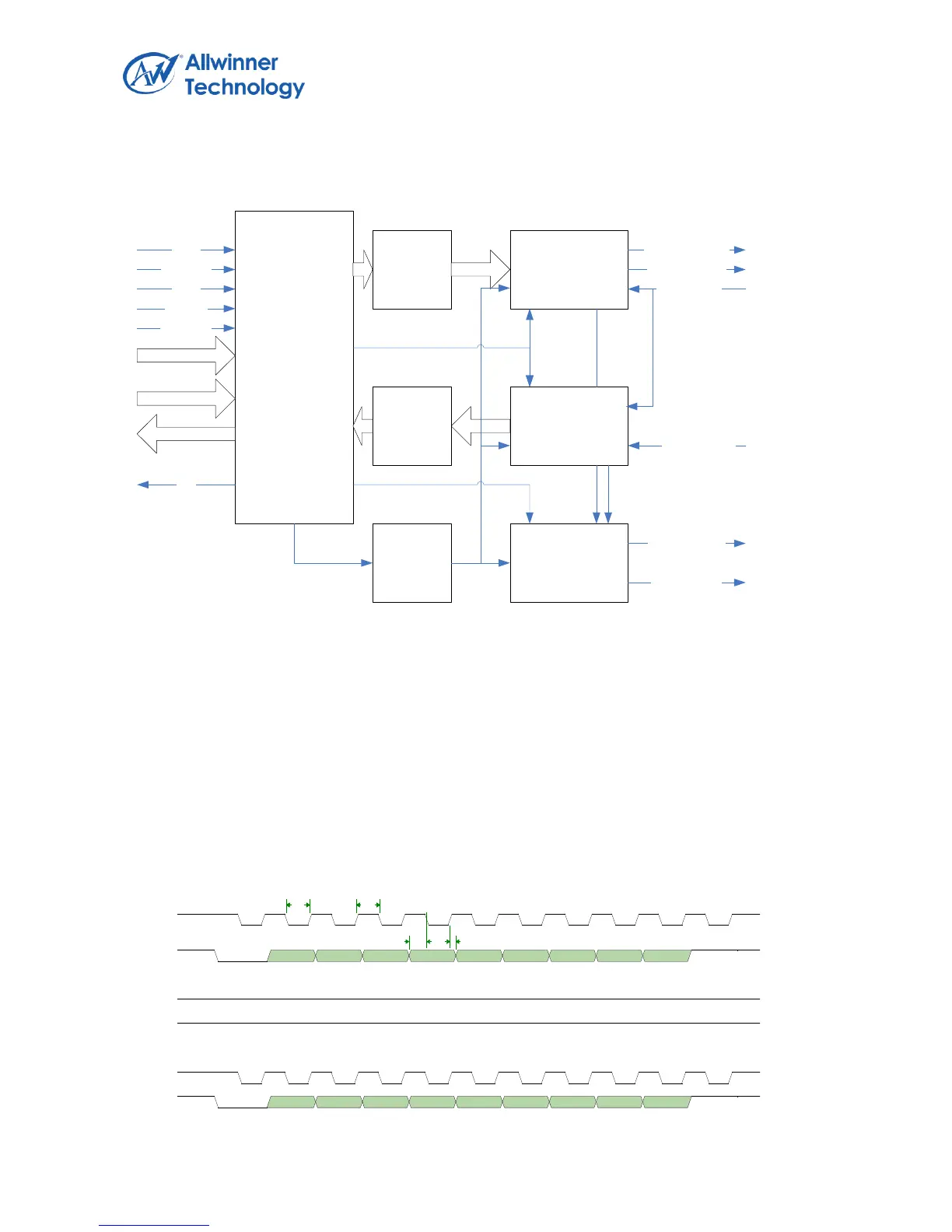

6.5.3. PS2 Timing Diagram

The Data and Clock lines of PS2 Bus are both open-collector with pull-up resistors to power, and so,

Data and Clock signals on PS2 Bus are both wire-and by corresponding signal of Host and Device.

Data is transferred after start bit, starting with the least significant bit(LSB). These are followed by the

parity bit, followed by one stop bit. If data is transferred from master to device, there is an additional

acknowledge bit(ACK) sent by device, following the stop bit.

Timing for Device Transmit Data and Master Receive Data:

Loading...

Loading...