A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 632 / 812

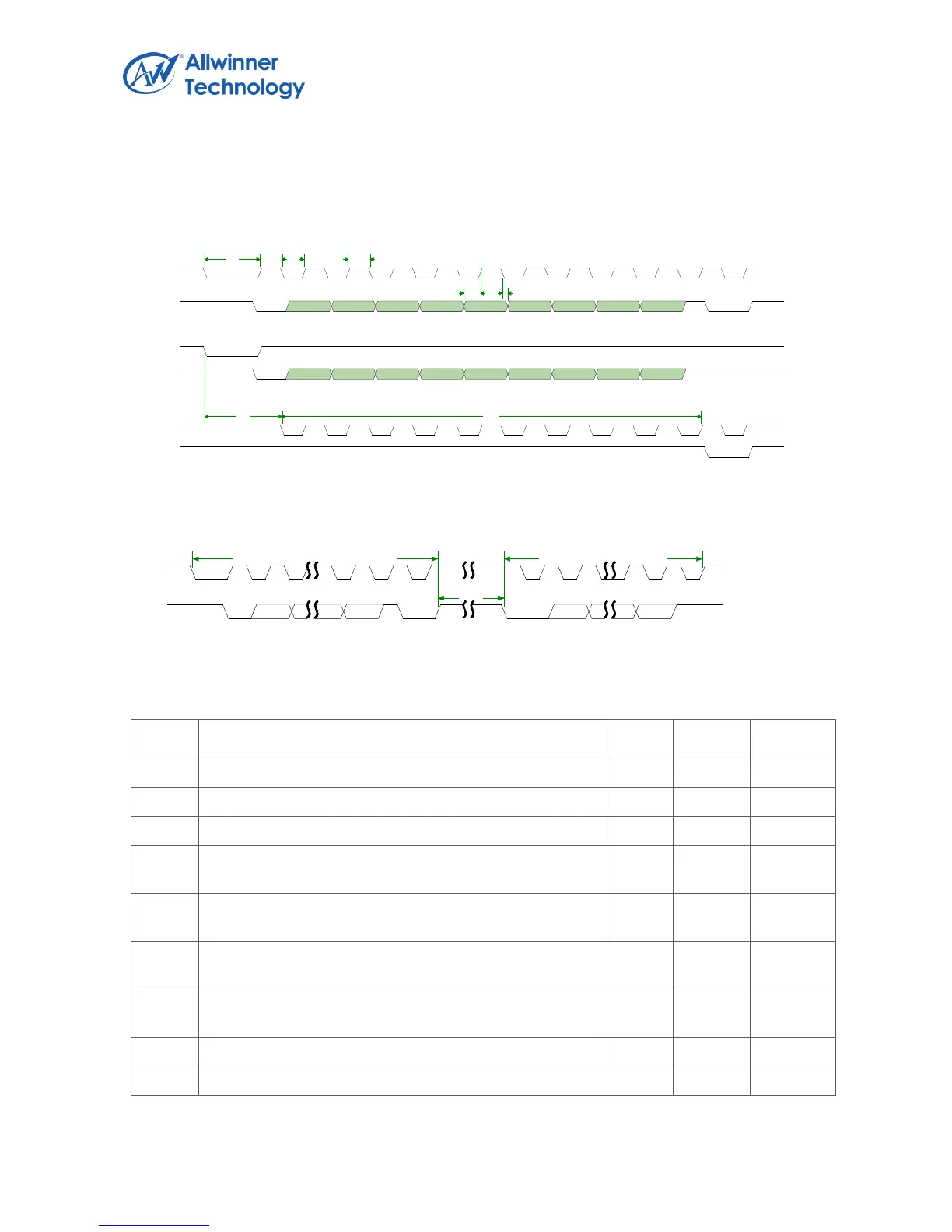

Timing for Master Transmit Data and Device Receive Data:

TdataTdataTc2c

Tf2dTd2r

TckhTckhTcklTcklTinhTinh

CLOCK

DATA

HOST_CLOCK

HOST_DATA

DEVICE_CLOCK

DEVICE_DATA

Timing for Master sending command then Device sending response

Host sends command to device

Device drive and sample data at rising edge of CLOCK. Master drive and sample data at falling edge

of CLOCK.

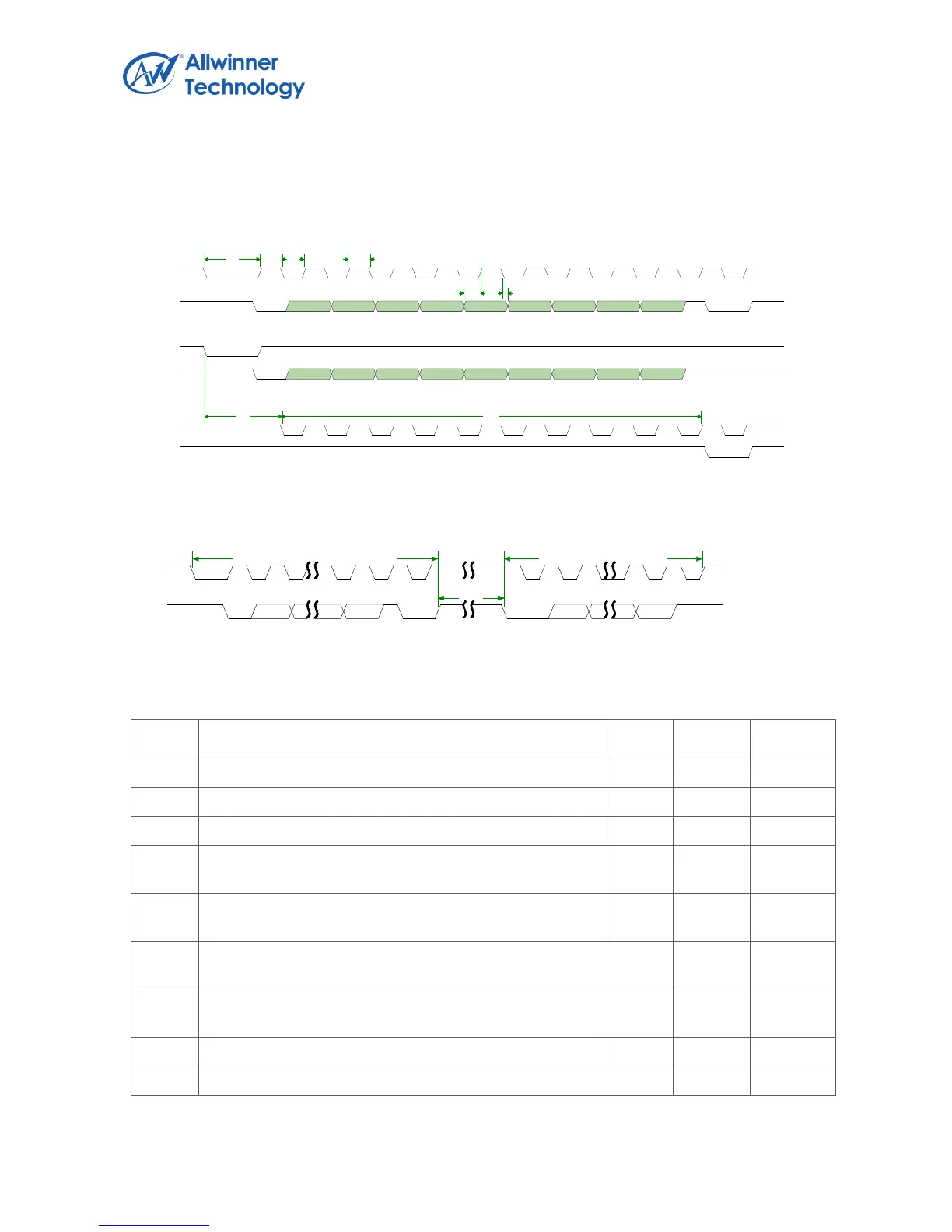

Time for Host inhibit clock for send data request

Data change to clock falling edge time during device to

host transfer

Clock rising edge to data change time during device to

host transfer

Data change to clock rising edge time during host to

device transfer

Clock falling edge to data change time during host to

device transfer

Host pull low Clock to Device drive Clock

Loading...

Loading...