A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 313 / 812

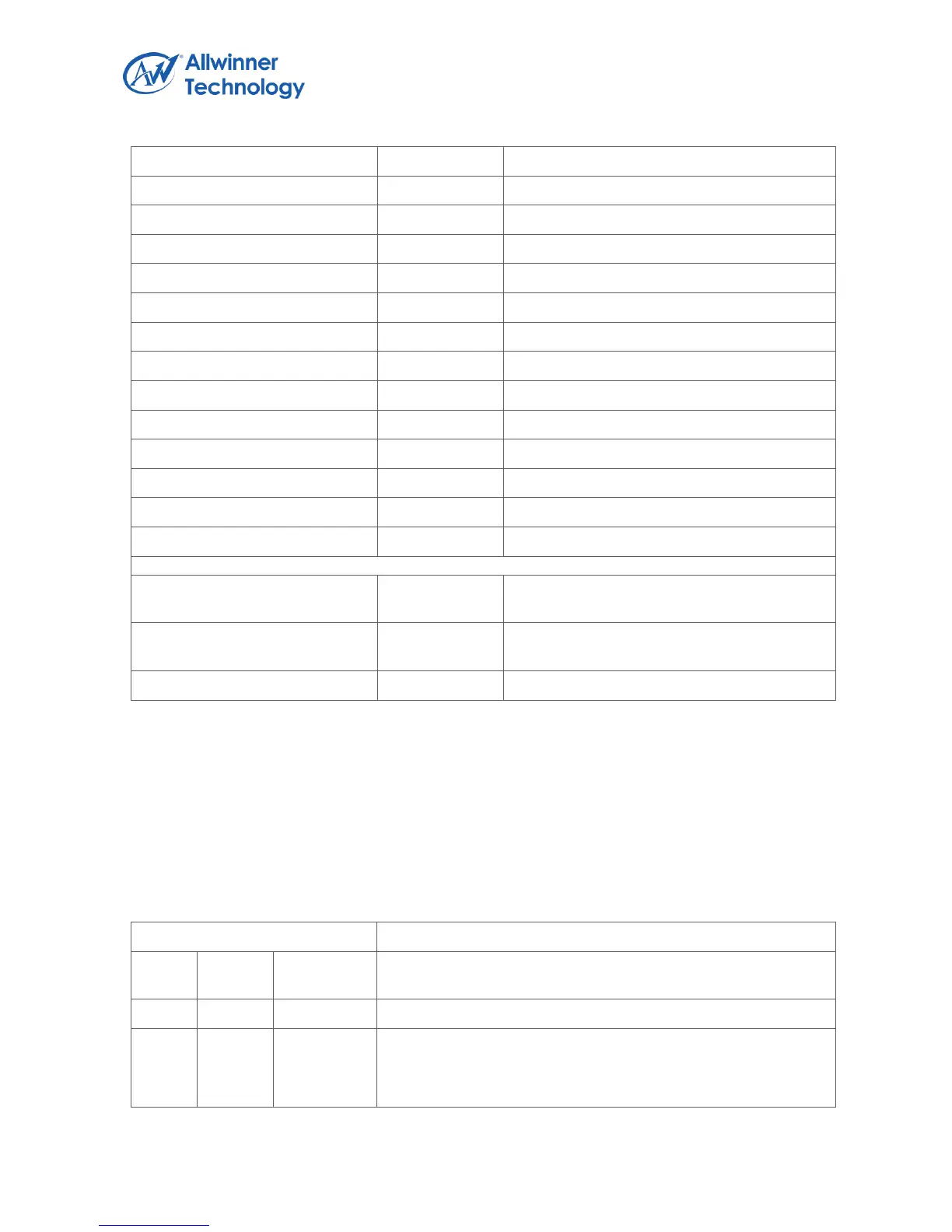

Output alpha control register

CSC0/1 Y/G coefficient register

CSC0/1 Y/G constant register

CSC0/1 U/R coefficient register

CSC0/1 U/R constant register

CSC0/1 V/B coefficient register

CSC0/1 V/B constant register

CSC2 Y/G coefficient register

CSC2 Y/G constant register

CSC2 U/R coefficient register

CSC2 U/R constant register

CSC2 V/B coefficient register

CSC2 V/B constant register

Scaling horizontal filtering coefficient RAM

block

Scaling vertical filtering coefficient RAM

block

3.1.4. MP Register Description

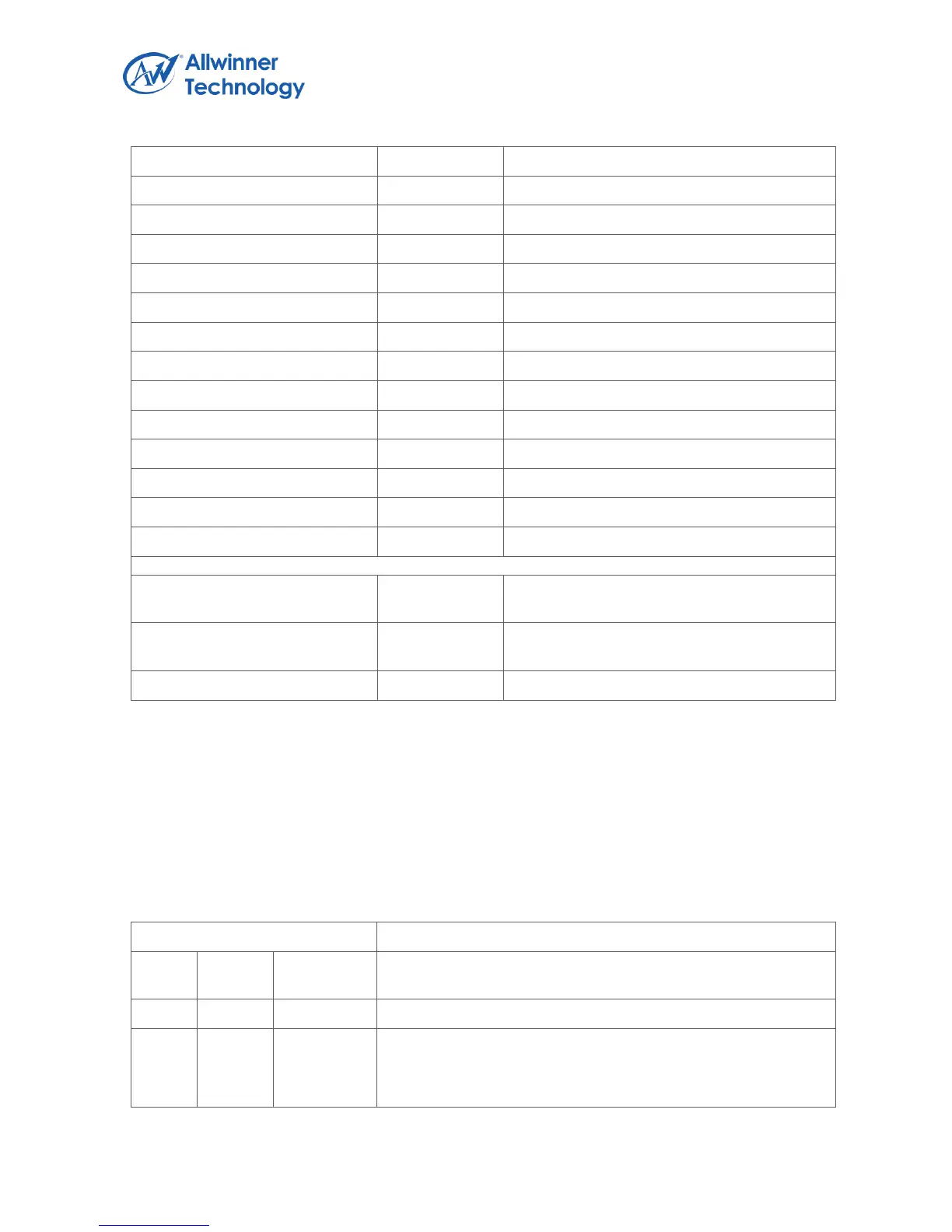

3.1.4.1. MIXER CONTROL REGISTER

Register Name: MP_CTL_REG

HWERRIRQ_EN

Hardware error IRQ enable control

0:disable

Loading...

Loading...