A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 578 / 812

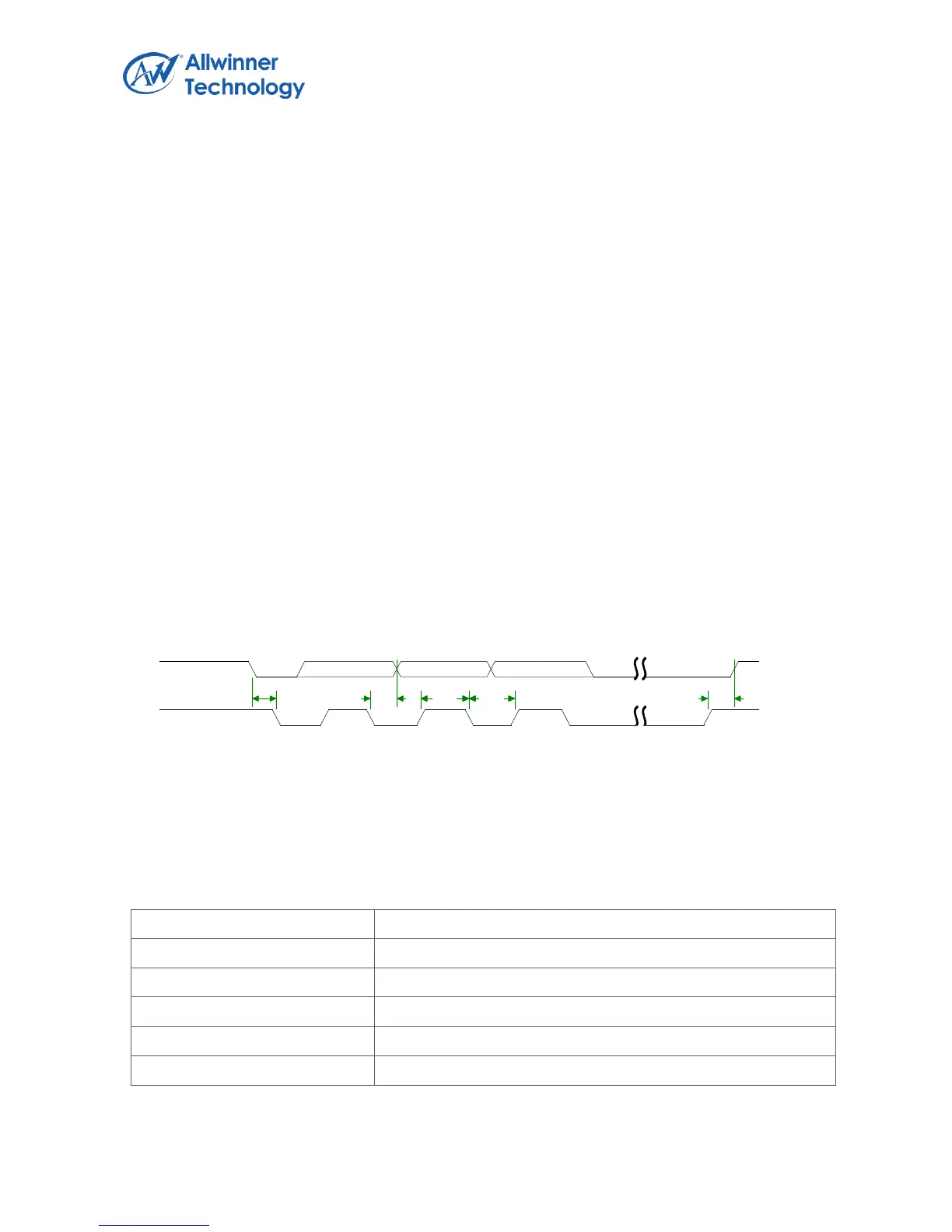

6.2.2. TWI Controller Timing Diagram

Data transferred are always in a unit of 8-bit (byte), followed by an acknowledge bit. The number of

bytes that can be transmitted per transfer is unrestricted. Data is transferred in serial with the MSB

first. Between each byte of data transfer, a receiver device will hold the clock line SCL low to force the

transmitter into a wait state while waiting the response from microprocessor.

Data transfer with acknowledge is obligatory. The clock line is driven by the master all the time,

including the acknowledge-related clock cycle, except for the SCL holding between each bytes. After

sending each byte, the transmitter releases the SDA line to allow the receiver to pull down the SDA

line and send an acknowledge signal (or leave it high to send a “not acknowledge”) to the transmitter.

When a slave receiver doesn’t acknowledge the slave address (unable to receive because of no

resource available), the data line must be left high by the slave so that the master can then generate

a STOP condition to abort the transfer. Slave receiver can also indicate not to want to send more

data during a transfer by leave the acknowledge signal high. And the master should generate the

STOP condition to abort the transfer.

Following diagram provides an illustration the relation of SDA signal line and SCL signal line on the

2-Wire serial bus.

Loading...

Loading...