A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 626 / 812

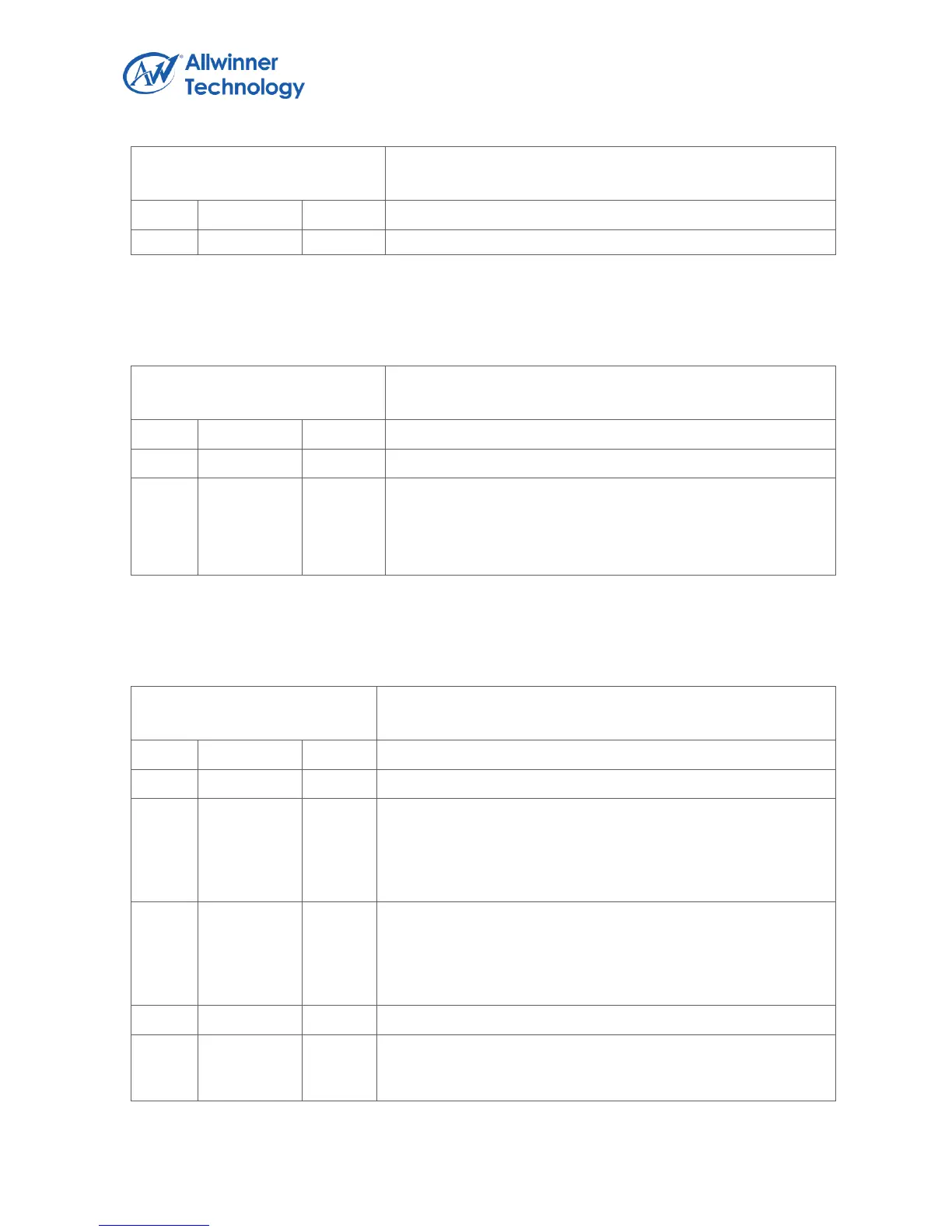

Register Name: UART_TFL

Default Value: 0x0000_0000

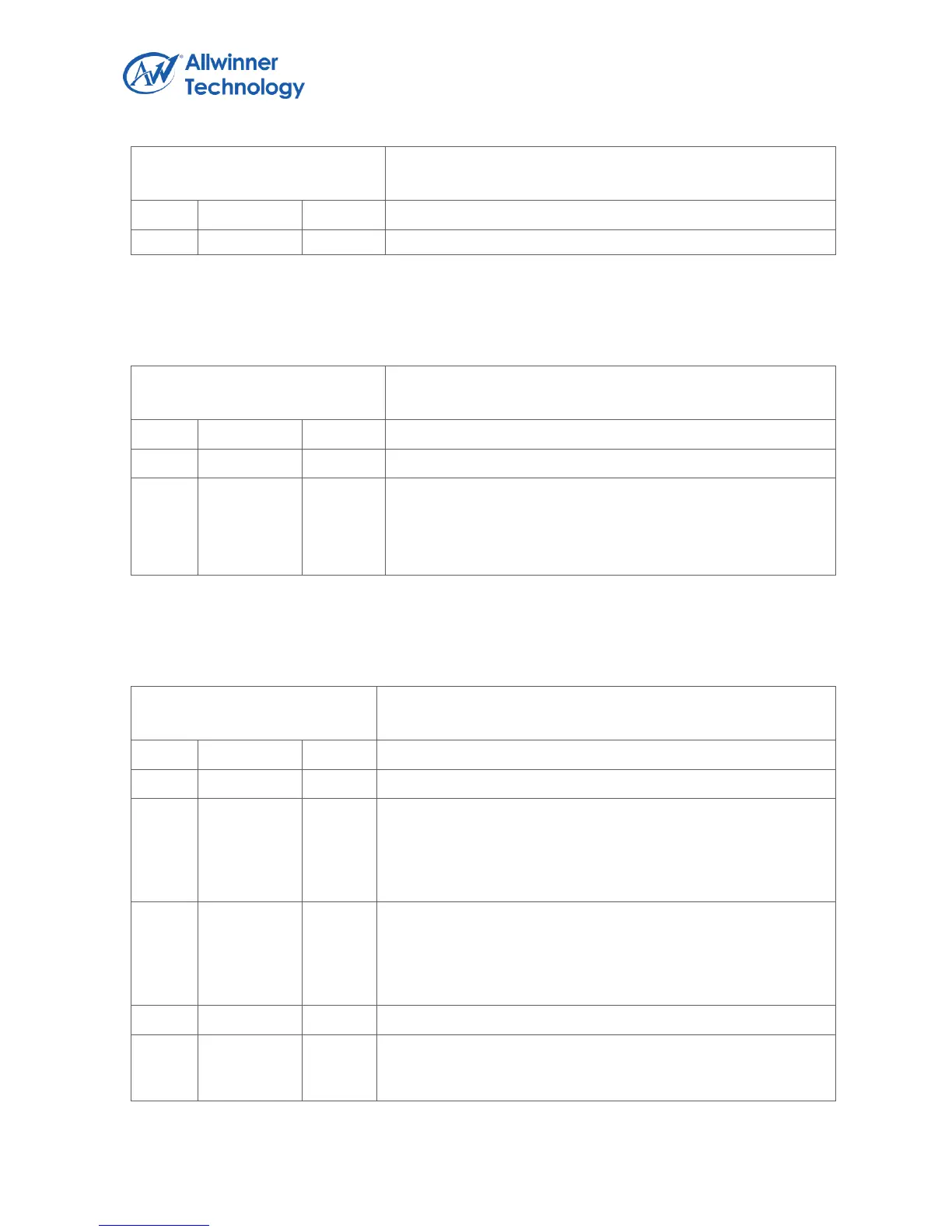

6.4.4.15. UART RECEIVE FIFO LEVEL REGISTER

Register Name: UART_RFL

Default Value: 0x0000_0000

RFL

Receive FIFO Level

This is indicates the number of data entries in the receive

FIFO.

6.4.4.16. UART HALT TX REGISTER

Register Name: UART_HALT

Default Value: 0x0000_0000

SIR_RX_INVERT

SIR Receiver Pulse Polarity Invert

0: Not invert receiver signal

1: Invert receiver signal

SIR_TX_INVERT

SIR Transmit Pulse Polarity Invert

0: Not invert transmit pulse

1: Invert transmit pulse

CHANGE_UPDATE

After the user using HALT[1] to change the baudrate or LCR

configuration, write 1 to update the configuration and waiting

Loading...

Loading...