A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 625 / 812

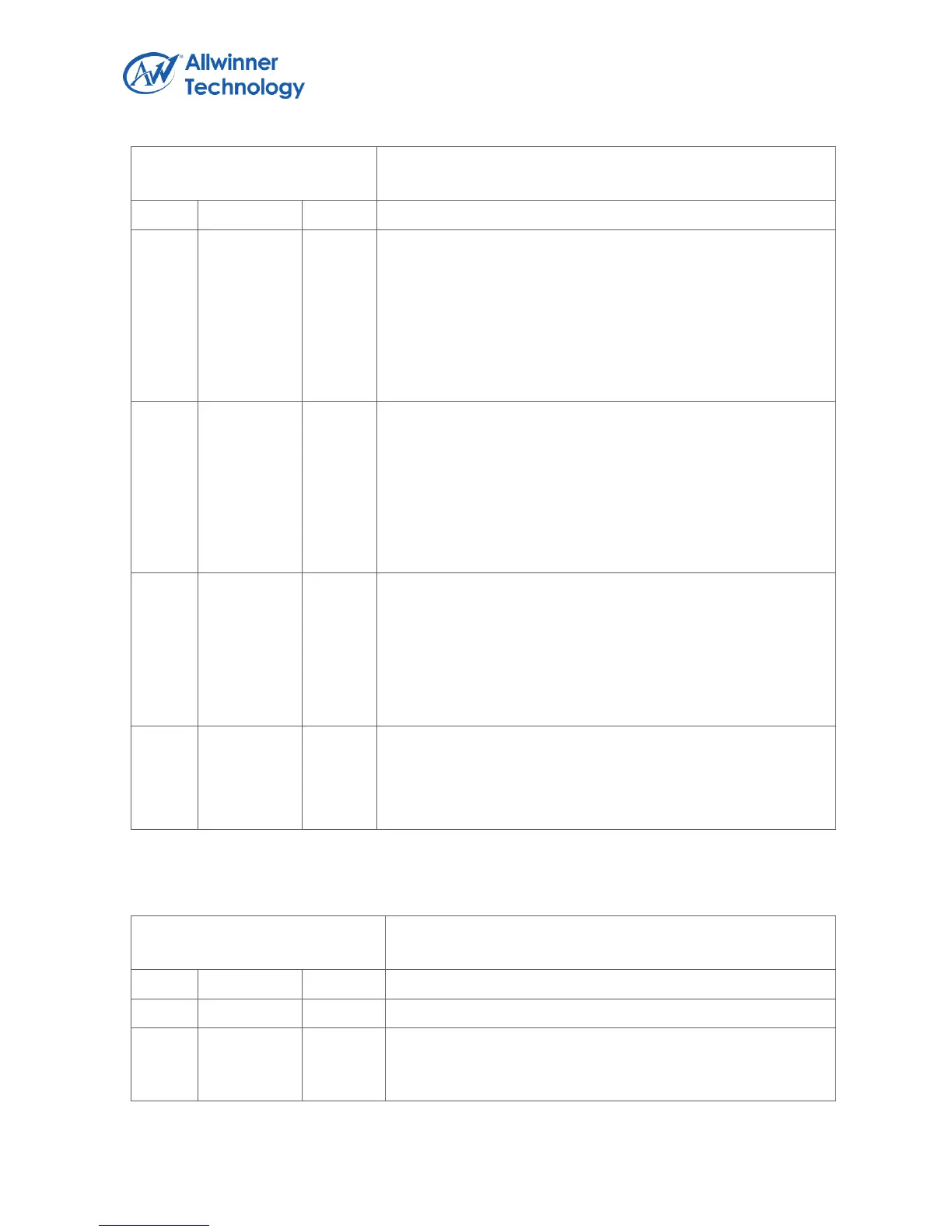

Register Name: UART_USR

Default Value: 0x0000_0006

RFNE

Receive FIFO Not Empty

This is used to indicate that the receive FIFO contains one or

more entries.

0: Receive FIFO is empty

1: Receive FIFO is not empty

This bit is cleared when the RX FIFO is empty.

TFE

Transmit FIFO Empty

This is used to indicate that the transmit FIFO is completely

empty.

0: Transmit FIFO is not empty

1: Transmit FIFO is empty

This bit is cleared when the TX FIFO is no longer empty.

TFNF

Transmit FIFO Not Full

This is used to indicate that the transmit FIFO in not full.

0: Transmit FIFO is full

1: Transmit FIFO is not full

This bit is cleared when the TX FIFO is full.

BUSY

UART Busy Bit

0: Idle or inactive

1: Busy

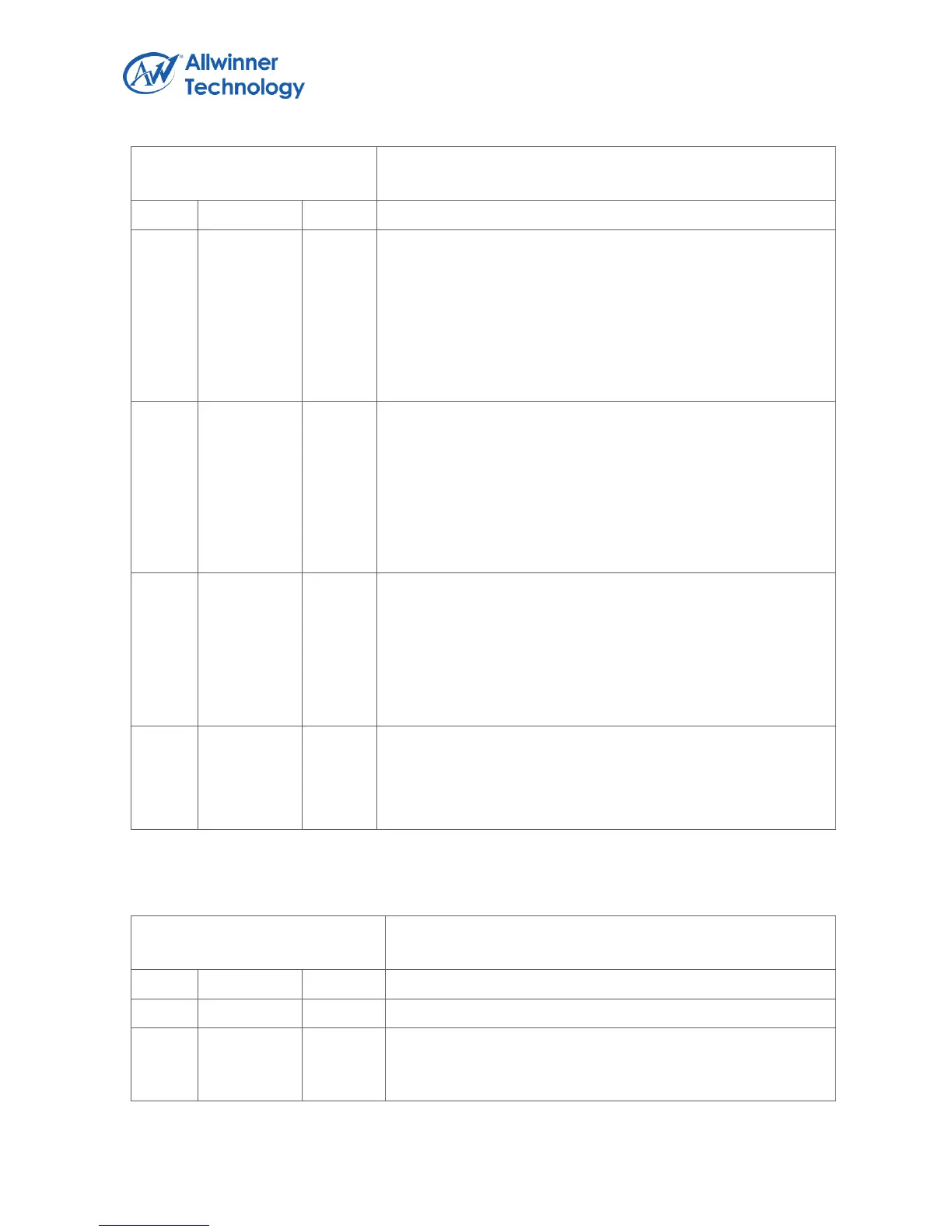

6.4.4.14. UART TRANSMIT FIFO LEVEL REGISTER

Register Name: UART_TFL

Default Value: 0x0000_0000

TFL

Transmit FIFO Level

This is indicates the number of data entries in the transmit

Loading...

Loading...