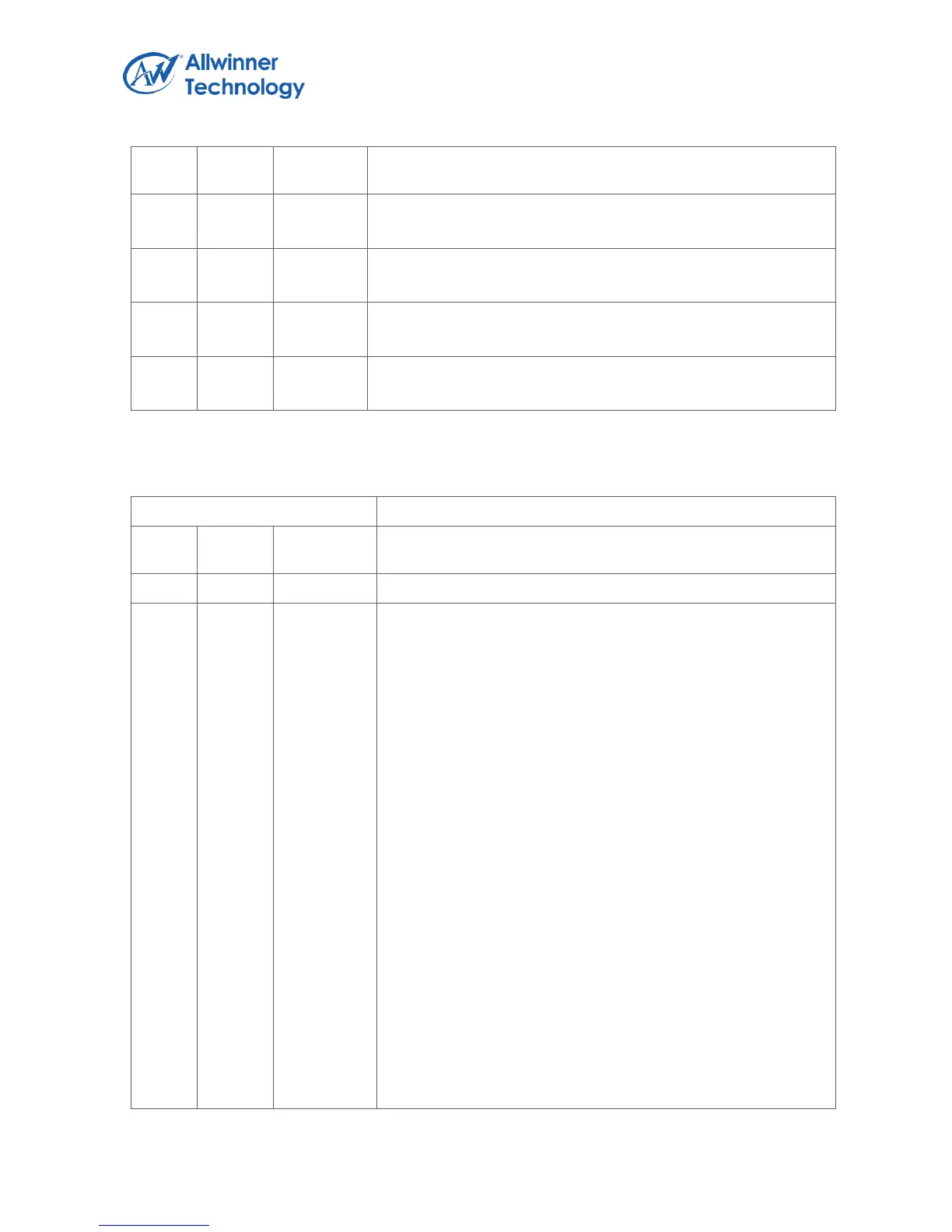

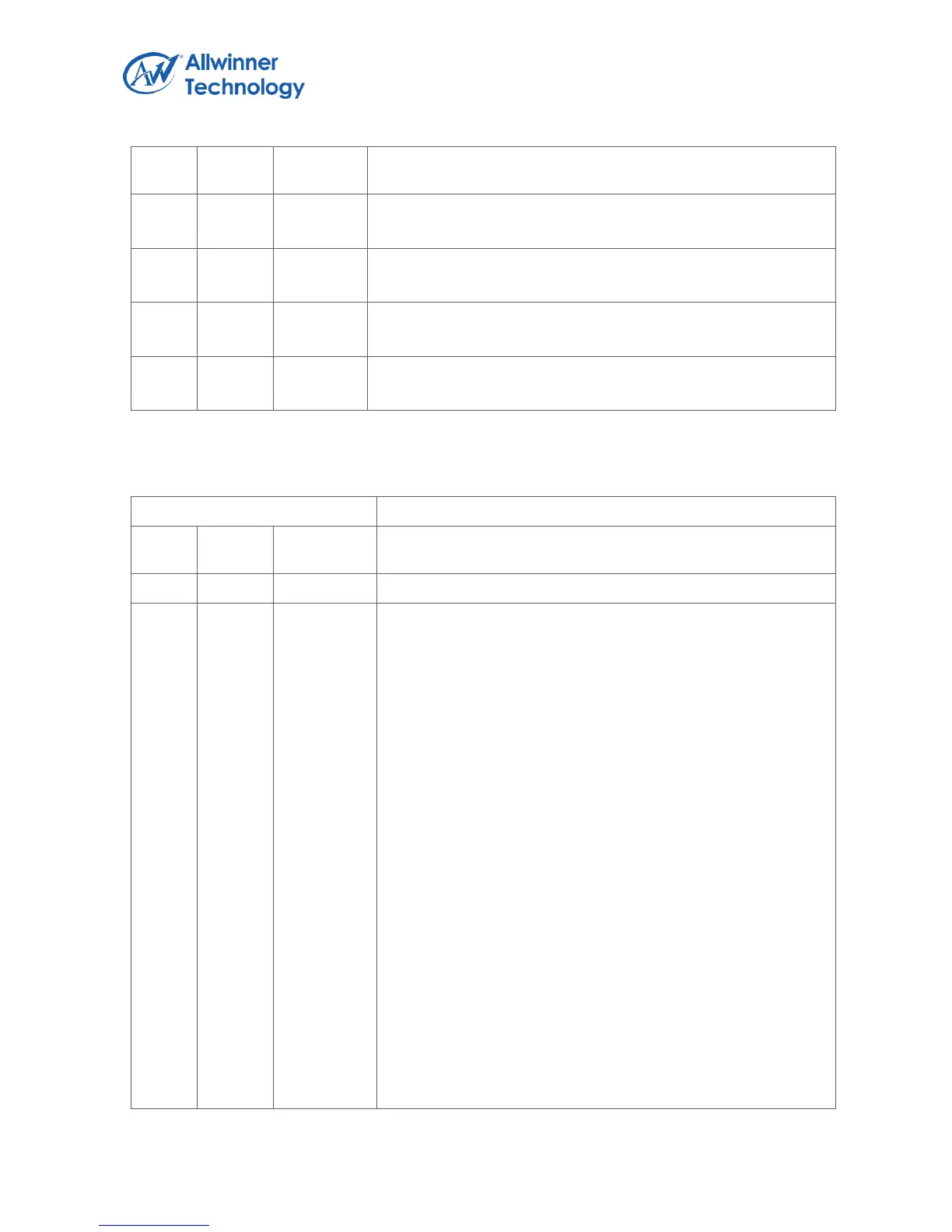

CSC0_DATAMOD

Data mode control

0:

Interleaved AYUV8888 mode

1:

Interleaved YUV422 mode

In mode 0 and mode 1, only the channel 0 data path is valid

for this module, the channel 1 data flow will by-pass the csc0

module, and direct to input formatter 1.

2:

Planar YUV422 mode (UV combined only)

3:

Planar YUV420 mode (UV combined only)

4:

Planar YUV411 mode (UV combined only)

In mode 2/3/4, following rule:

----Y component data transfer through channel 0, and UV

component data transfer through channel 1.

Loading...

Loading...