A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 640 / 812

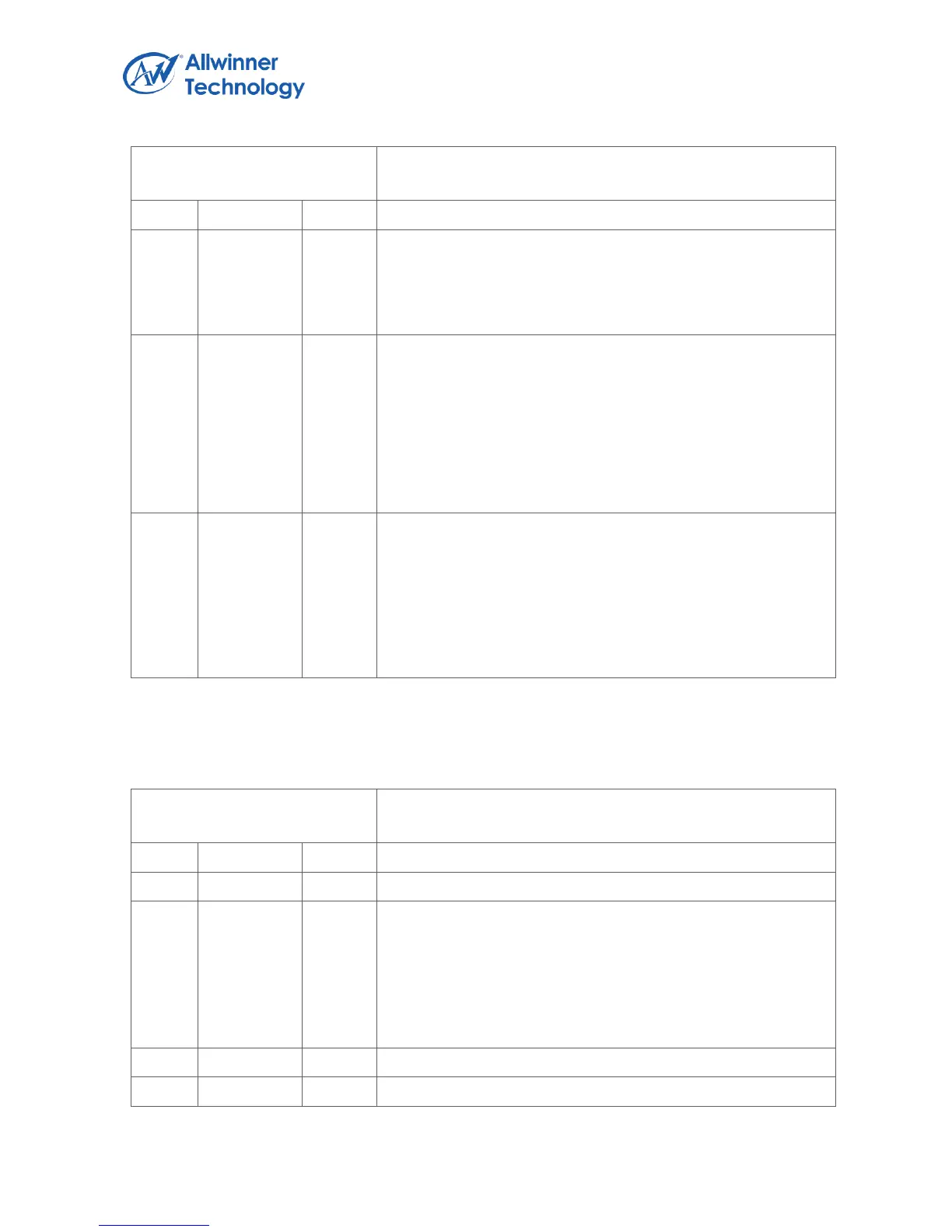

Register Name: PS2_FSTS

Default Value: 0x0000_0100

the RXFIFO is read by CPU after empty. This bit is just a flag

of illegal operation, which should not affect any state of

RXFIFO.

Note: This bit can be cleared by writing ‘1’, writing ‘0’ has no

effect.

RX_OF

RXFIFO Overflow

When this bit is set, RXFIFO is overflow, and it means that the

RXFIFO is wrote by receive engine after RXFIFO is full. This

bit is just a flag of illegal operation, which should not affect any

state of RXFIFO.

Note: This bit can be cleared by writing ‘1’, writing ‘0’ has no

effect.

RX_RDY

Receive Ready

0 – RXFIFO is empty

1 – RXFIFO is not empty, there are at least one byte data,

which is received from PS2 bus, in the RXFIFO.

Note: This bit can be cleared by writing ‘1’, writing ‘0’ has no

effect.

6.5.5.7. PS2 CLOCK DIVIDER REGISTER

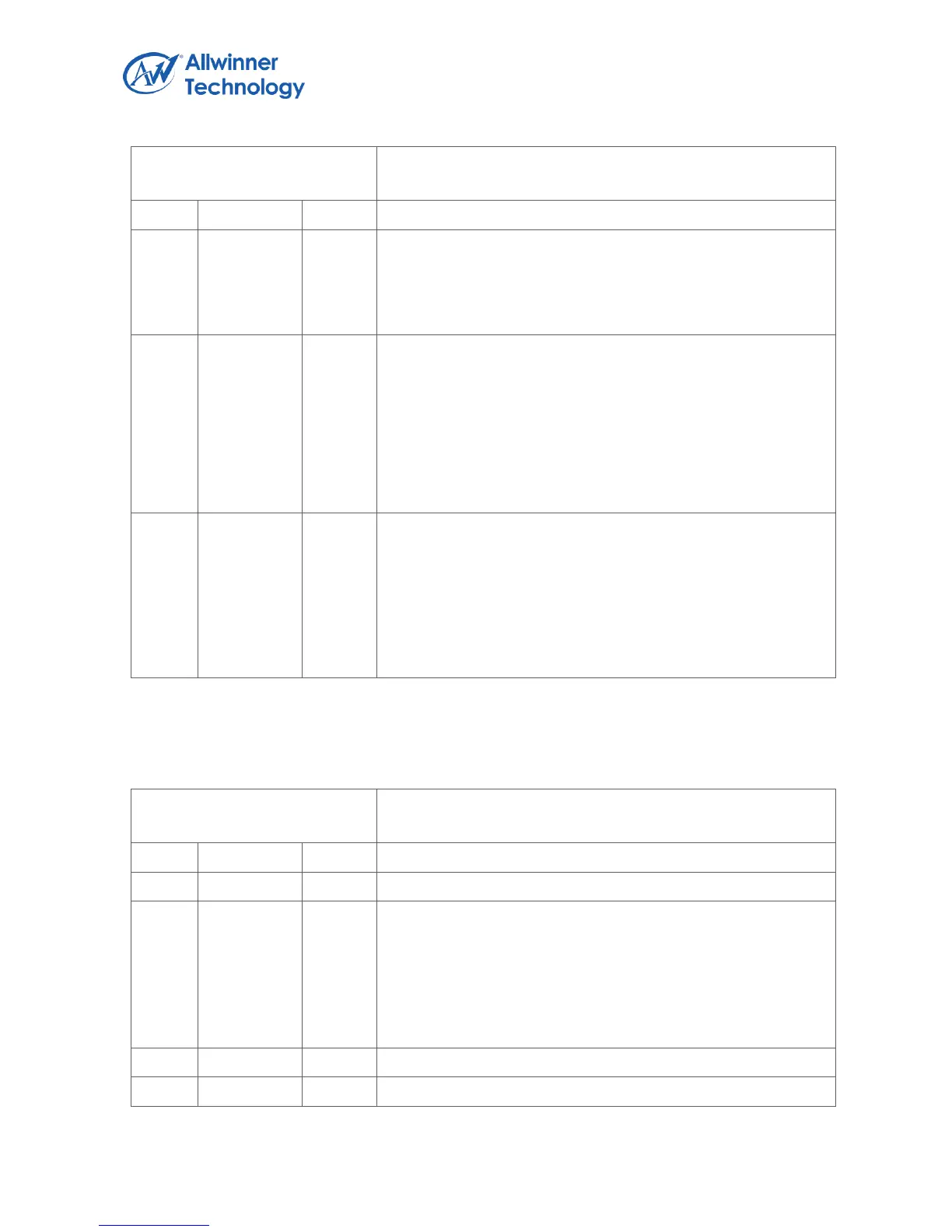

Register Name: PS2_CKDR

Default Value: 0x0000_2F4F

SCLK_DIV

Sample Clock Divider Factor (SCDF)

Sample Clock is a 1MHz clock for internal timing control.

SCDF = APB_CLK/SAMPLE_CLK – 1

Frequency of sample clock is constant, and so, frequency of

APB_CLK must be in the range 1-256MHz.

Loading...

Loading...