A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 689 / 812

FrameNumber

This is incremented when HcFmRemaining is re-loaded. It will be

rolled over to 0x0 after 0x0ffff. When entering the

USBOPERATIONAL state, this will be incremented automatically.

The content will be written to HCCA after HC has incremented the

FrameNumber at each frame boundary and sent a SOF but before

HC reads the first ED in that Frame. After writing to HCCA, HC will

set the StartofFrame in HcInterruptStatus.

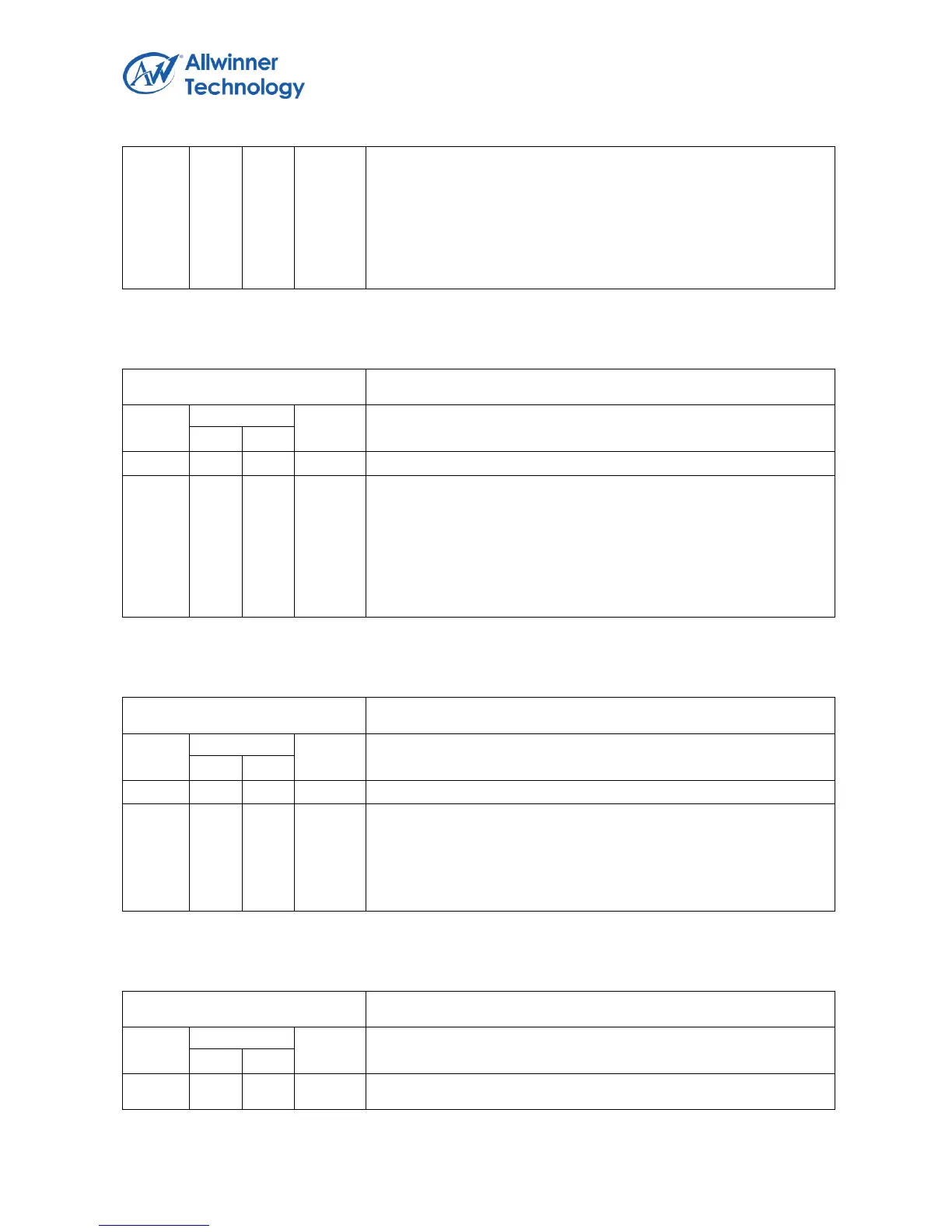

6.8.7.17. HCPERIODICSTART REGISTER

Register Name: HcPeriodicStatus

Default Value: 0x0

PeriodicStart

After a hardware reset, this field is cleared. This is then set by HCD

during the HC initialization. The value is calculated roughly as 10%

off from HcFmInterval.. A typical value will be 0x3e67. When

HcFmRemaining reaches the value specified, processing of the

periodic lists will have priority over Control/Bulk processing. HC will

therefore start processing the Interrupt list after completing the

current Control or Bulk transaction that is in progress.

6.8.7.18. HCLSTHRESHOLD REGISTER

Register Name: HcLSThreshold

Default Value: 0x0628

LSThreshold

This field contains a value which is compared to the

FrameRemaining field prior to initiating a Low Speed transaction.

The transaction is started only if FrameRemaining >= this field.

The value is calculated by

HCD with the consideration of transmission and setup overhead.

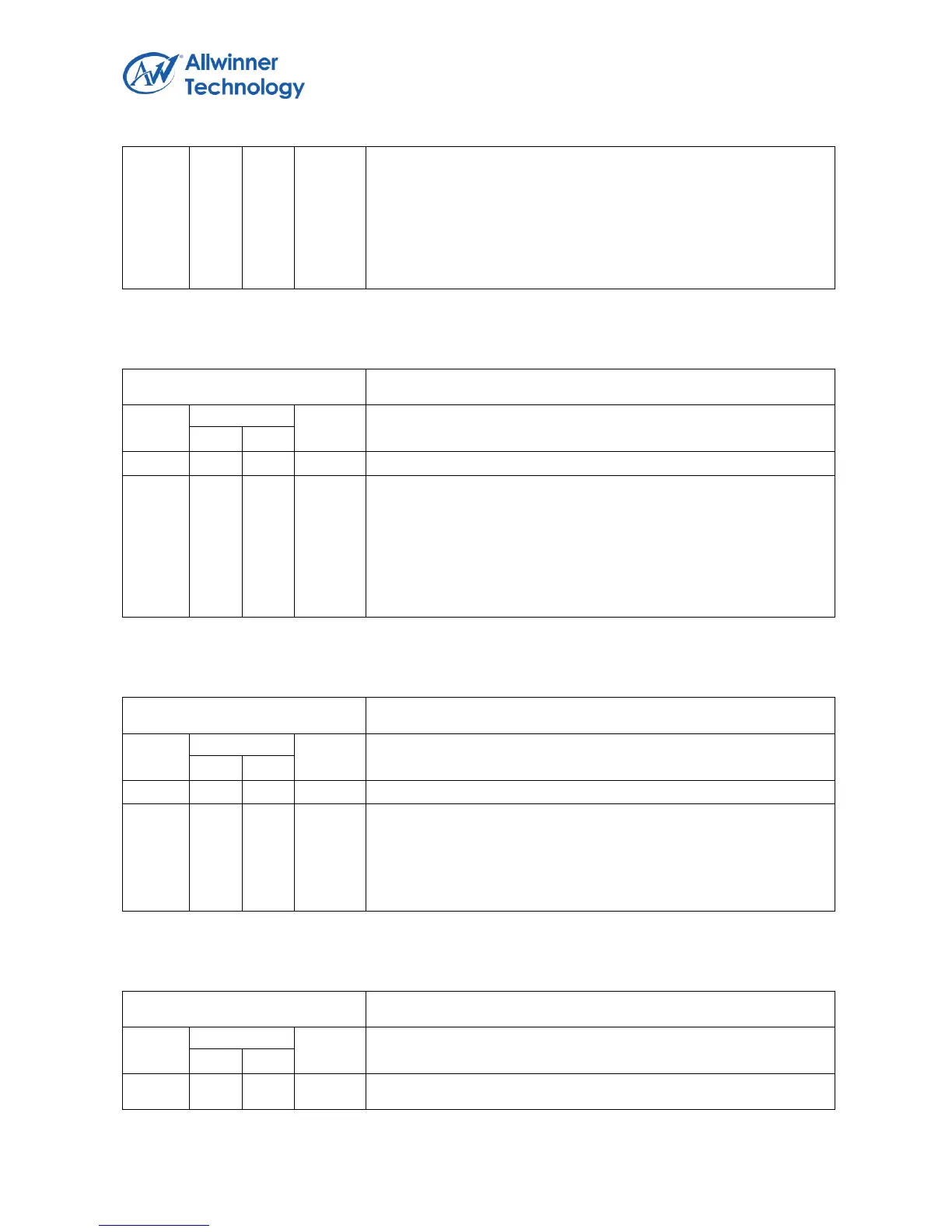

6.8.7.19. HCRHDESCRIPTORA REGISTER

Register Name: HcRhDescriptorA

Default Value:0x02001201

PowerOnToPowerGoodTime[POTPGT]

This byte specifies the duration HCD has to wait before accessing

Loading...

Loading...