A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 795 / 812

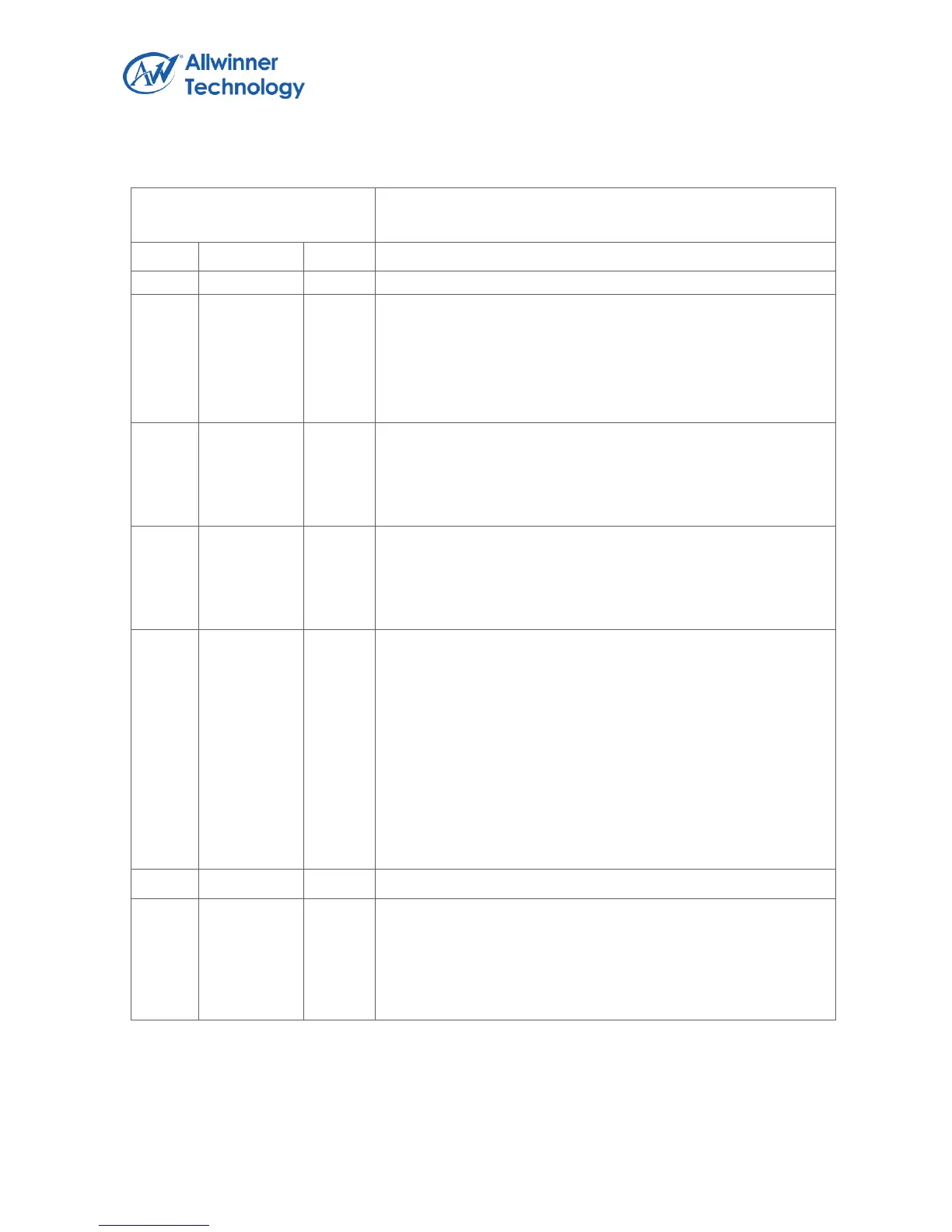

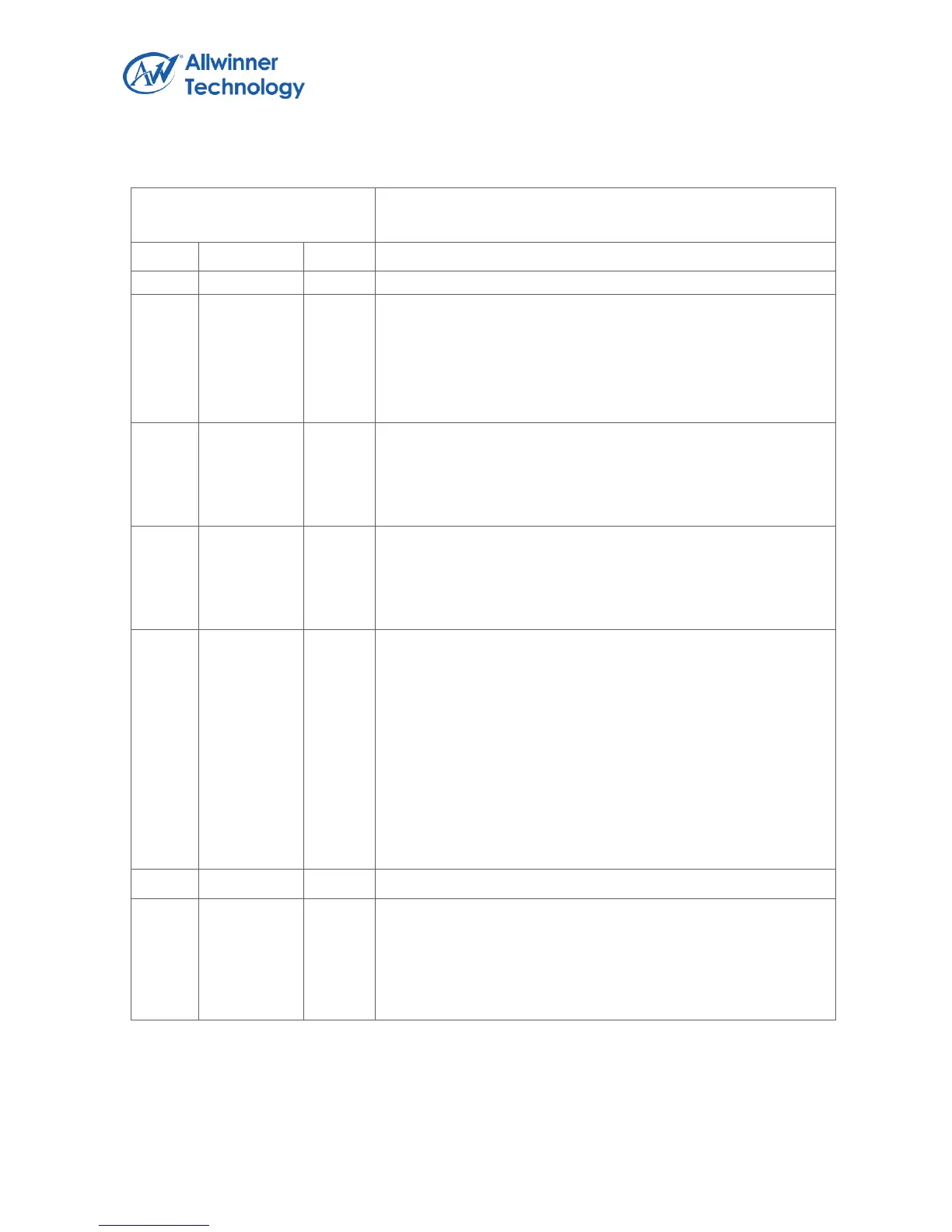

6.16.5.6. CAN BUS TIMING REGISTER

Register Name:

CAN_BUS_TIME

Default Value: 0x0000_0000

SAM

Sample Point Control

0 – Bus line is sampled once at the sample point

1 – Bus line is sampled three times at the sample point

This bit is only writable in reset mode.

PHSEG2

Phase Segment 2

[0..7] – [1..8] Tq clock cycle(s)

These bits are only writable in reset mode.

PHSEG1

Phase Segment 1

[0..15] – [1..16] Tq clock cycle(s)

These bits are only writable in reset mode.

SJW

Synchronization Jump Width

The SJW defines the maximum number of Tq clock cycles a bit

can be shortened or lengthened to achieve resynchronization

to data transitions on the bus.

0 – 1 Tq clock cycle

1 – 2 Tq clock cycles

2 – 3 Tq clock cycles

3 – 4 Tq clock cycles

These bits are only writable in reset mode.

TQ_BRP

Time Quanta Baud Rate Prescaler

These bits determine the time quanta (Tq) clock which is used

to build up the individual bit timing.

These bits are only writable in reset mode.

Loading...

Loading...