315

1

2

M

3

○ ○ ○○

FNC

189

S : the source device to be transferred

D : the destination device

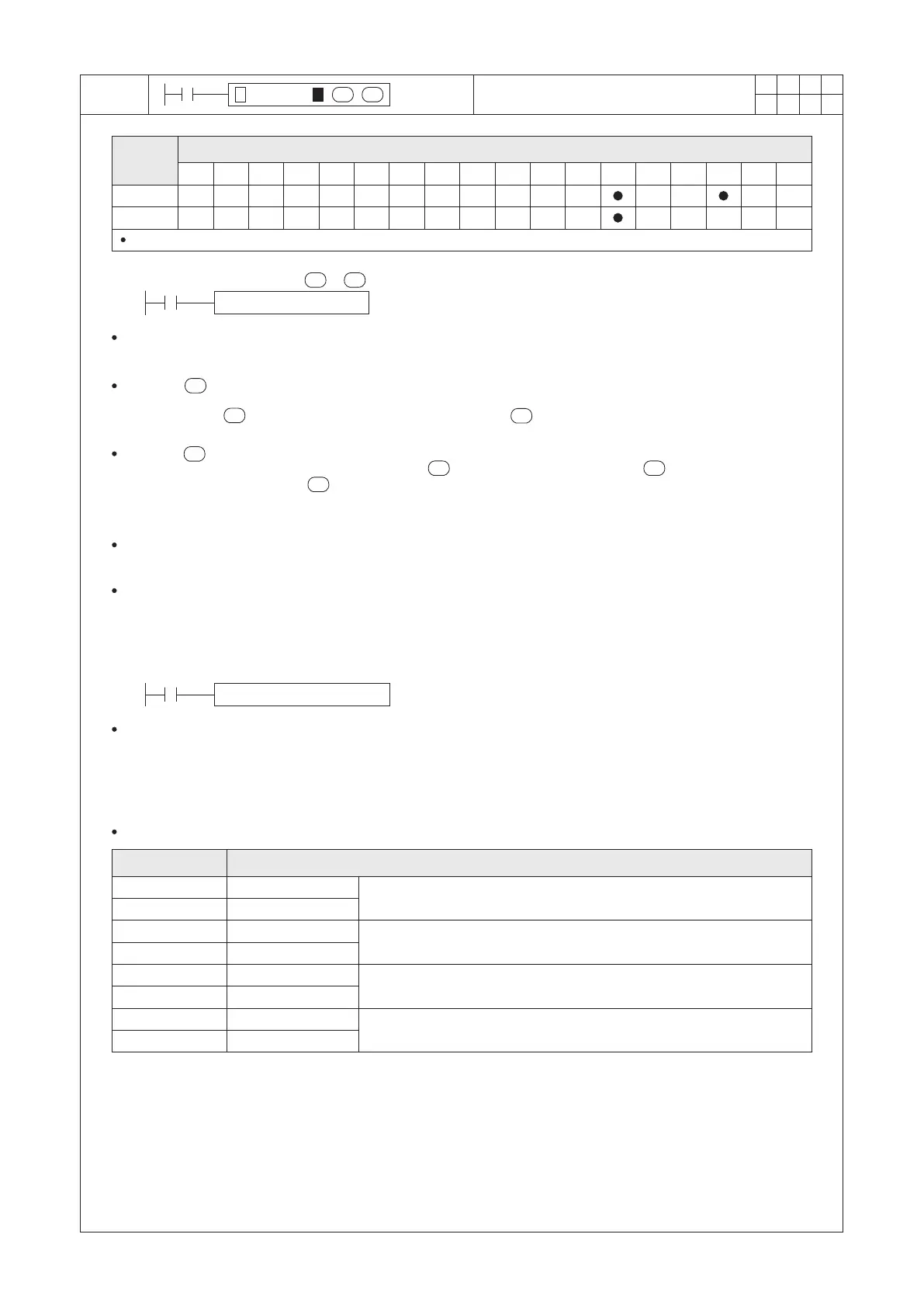

DHHCMVP D9226 D0

X20

D

S

X Y M S

D.b R.b

KnX KnY

KnM KnS

T C

D,R

V,Z

UnG

K,H

E

" $"

S

D

When the S or D is assigned to a HHSC related Special Register, not has the V, Z index function.

S

D

D

S

D

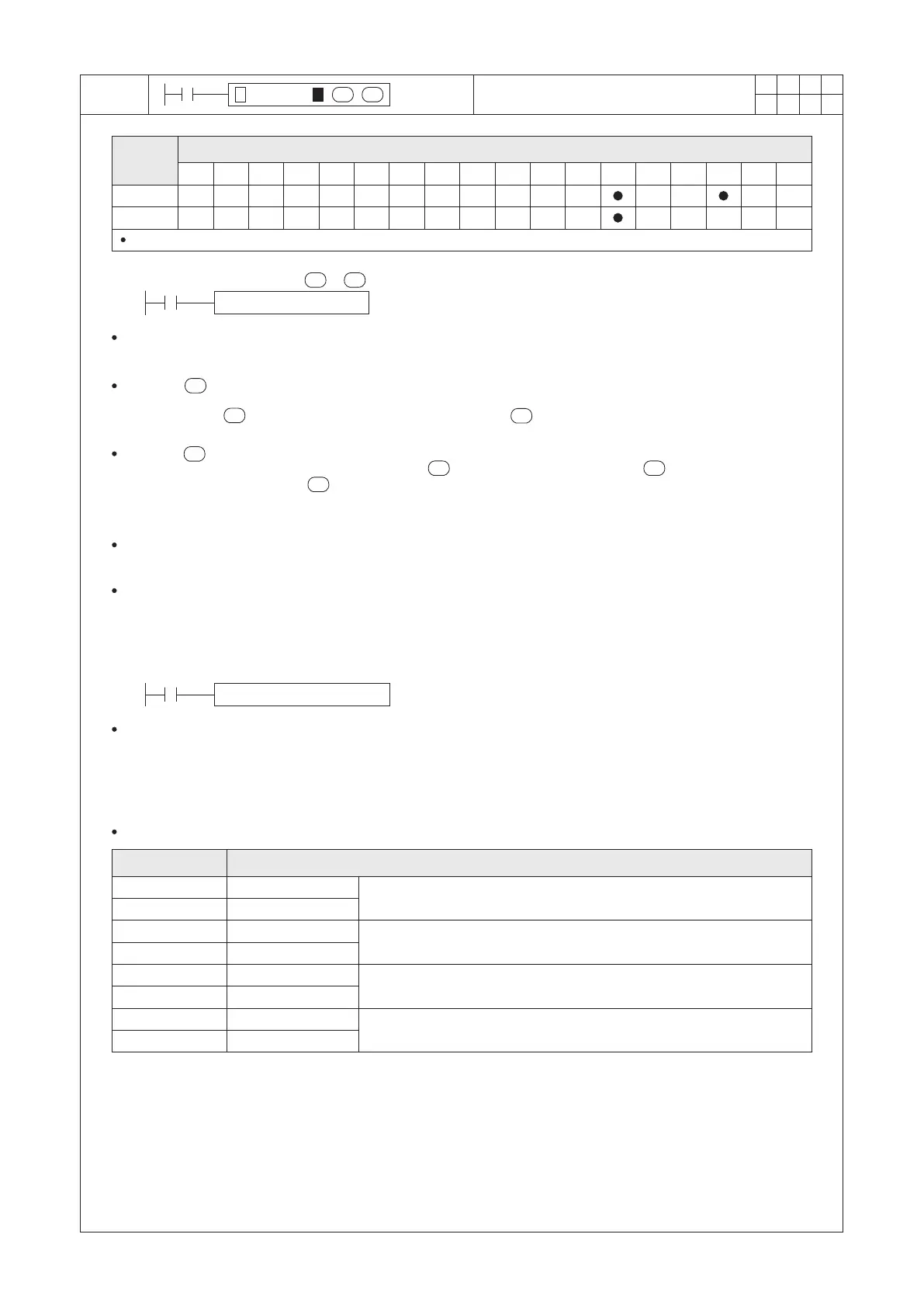

DHHCMVP K1000 D9230

X21

D9227

D9228

D9226

D9229

D9230

D9231

D9232

D9233

Operand

Devices

Hardware High-Speed Counter Data Move

S

D

When the is assigned to a HHSC's related Special Register, the PLC’s CPU will process the following

procedure. First, reads the data from the related hardware circuit. Second, stores the data to the specic

Special Register . Last, transmits the data to the designated . Thus, the value at the HHSC can be read

instantly.

When the is assigned to a HHSC's related Special Register, the PLC’s CPU will process the following

procedure. It copies the data from the designated to the specic Special Register , then duplicates the

data from the Special Register to the related hardware circuit.

The writable object of the process is the set value or present value of the HHSC. Thus, the set value or present

value at the HHSC can be write instantly.

This DHHCMV is a special instruction for to instantly read the content value of the Hardware High Speed Counter

(HHSC), or to instantly write a new content value or set-point value onto the HHSC.

When X21 = “OFF” → “ON”, the Special Register (D9231, D9230) and the set value at the hardware circuit of

HHSC1 will be written by the constant K1000.

When X20 = “OFF” → “ON”, the present value at the hardware circuit of HHSC1 will be read and store to the

Special Register (D9227, D9226) and the destination register (D1, D0).

This instruction is a 32-bit instruction. Therefore, be sure to input DHHCMV or DHHCMVP in the program.

The related special devices are summarized below:

Register ID No.

Description

Lower 16 bits

Upper 16 bits

Lower 16 bits

Lower 16 bits

Lower 16 bits

Upper 16 bits

Upper 16 bits

Upper 16 bits

The present value of HHSC1.

The present value of HHSC2.

The set value of HHSC1.

The set value of HHSC2.

D H H C M V P

D

S

Loading...

Loading...