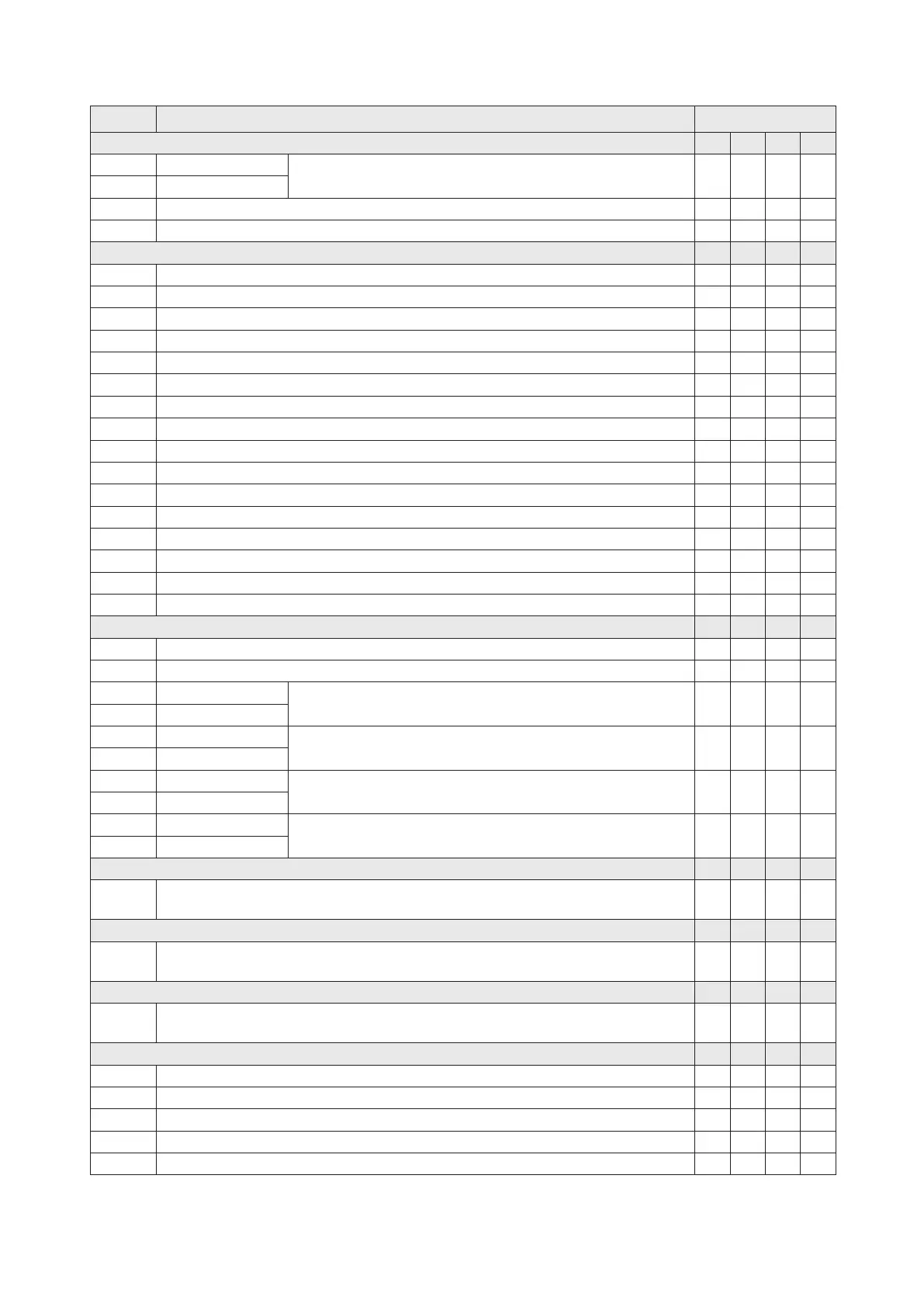

VS1 VS2 VSM

VS3

Index Register V, Z

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

D9180

D9183

D9181

D9184

D9182

D9185

D9186

D9187

D9188

D9189

D9190

D9191

D9192

D9193

D9194

D9195

Z0 Index Register

V0 Index Register

Z1 Index Register

V1 Index Register

Z2 Index Register

V2 Index Register

Z3 Index Register

V3 Index Register

Z4 Index Register

V4 Index Register

Z5 Index Register

V5 Index Register

Z6 Index Register

V6 Index Register

Z7 Index Register

V7 Index Register

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

○

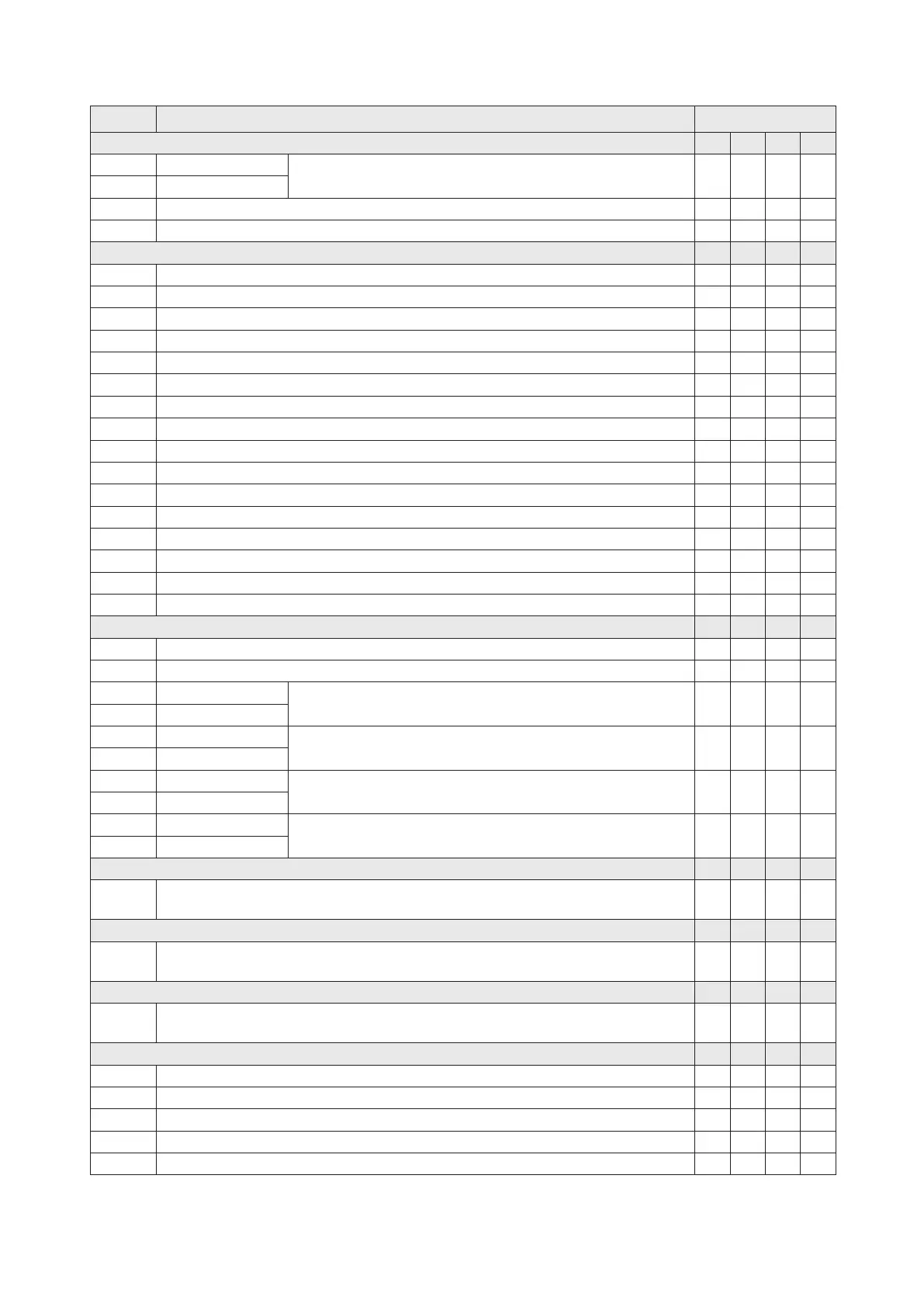

Hardware High Speed Counter

VS1 VS2 VSM

VS3

○

○

○

○

○

○

D9224

D9227

D9225

D9228

D9226

D9229

D9230

D9231

D9232

D9233

○○○

○○○

○

○

○

○

○

○

○

○

○

○

○

○

HHSC1 counting mode selection. “0” is to disable the HHSC1; “1” ~ “6” represent different modes.

VS1

VS1

VS1

VS2

VS2

VS2

VSM

VSM

VSM

VS3

VS3

VS3

Working Area of the EC1 Expansion Card

Working Area of the EC2 Expansion Card

Working Area of the EC3 Expansion Card

○

○

○

○

○

○

○

○

○

○

○

○

EC1 Expansion Card's working area. D9260~D9279=EC1D0~EC1D19.

EC2 Expansion Card's working area. D9280~D9299=EC2D0~EC2D19.

EC2 Expansion Card's working area. D9300~D9319=EC3D0~EC3D19.

D9260

D9279

〜

D9280

D9299

〜

D9300

D9319

〜

VS1 VS2 VSM

VS3

RND, HSCT, INT

D9160

Providing a number for the RND (FNC184) instruction to produce a

random value. Initial value: K1

○○○

D9161

○

■

D9162

○○○

The number of count is activated at the table of HSCT instruction.

External interrupt delay time set value ( Unit: ms).

○

D9163

○○○

VS1 VS2 VSM

VS3

○

○

○

DUTY Instruction Output

○

○

■

D9330

■

D9331

■

D9332

■

D9333

■

D9334

49

○

Register

ID No.

Description

Series

Lower 16 bits

Upper 16 bits

Lower 16 bits

Upper 16 bits

Lower 16 bits

Lower 16 bits

Lower 16 bits

Upper 16 bits

Upper 16 bits

Upper 16 bits

HHSC2 counting mode selection. “0” is to disable the HHSC2; “1” ~ “6” represent different modes.

The present value of HHSC1.

The present value of HHSC2.

The set value of HHSC1.

The set value of HHSC2.

Cycle counter #1 for the timing sequence pulse generative instruction DUTY (FNC186).

Cycle counter #2 for the timing sequence pulse generative instruction DUTY (FNC186).

Cycle counter #3 for the timing sequence pulse generative instruction DUTY (FNC186).

Cycle counter #4 for the timing sequence pulse generative instruction DUTY (FNC186).

Cycle counter #5 for the timing sequence pulse generative instruction DUTY (FNC186).

Loading...

Loading...