Z8 Microcontrollers

ZiLOG Instruction Set

UM001601-0803 12-9

Instruction

Address

Mode

Op Code

Byte Flags Affected

and Operation dst src (Hex) C Z S V D H

POP dst R 50 – – – – – –

dst ← @SP IR 51

and SP ← SP + 1

PUSH src R 70 – – – – – –

SP ← SP – 1 IR 71

and @SP ← src

RCF C F 0 – – – – –

C ← 0

RET A F – – – – – –

PC ← @SP;

SP ← SP + 2

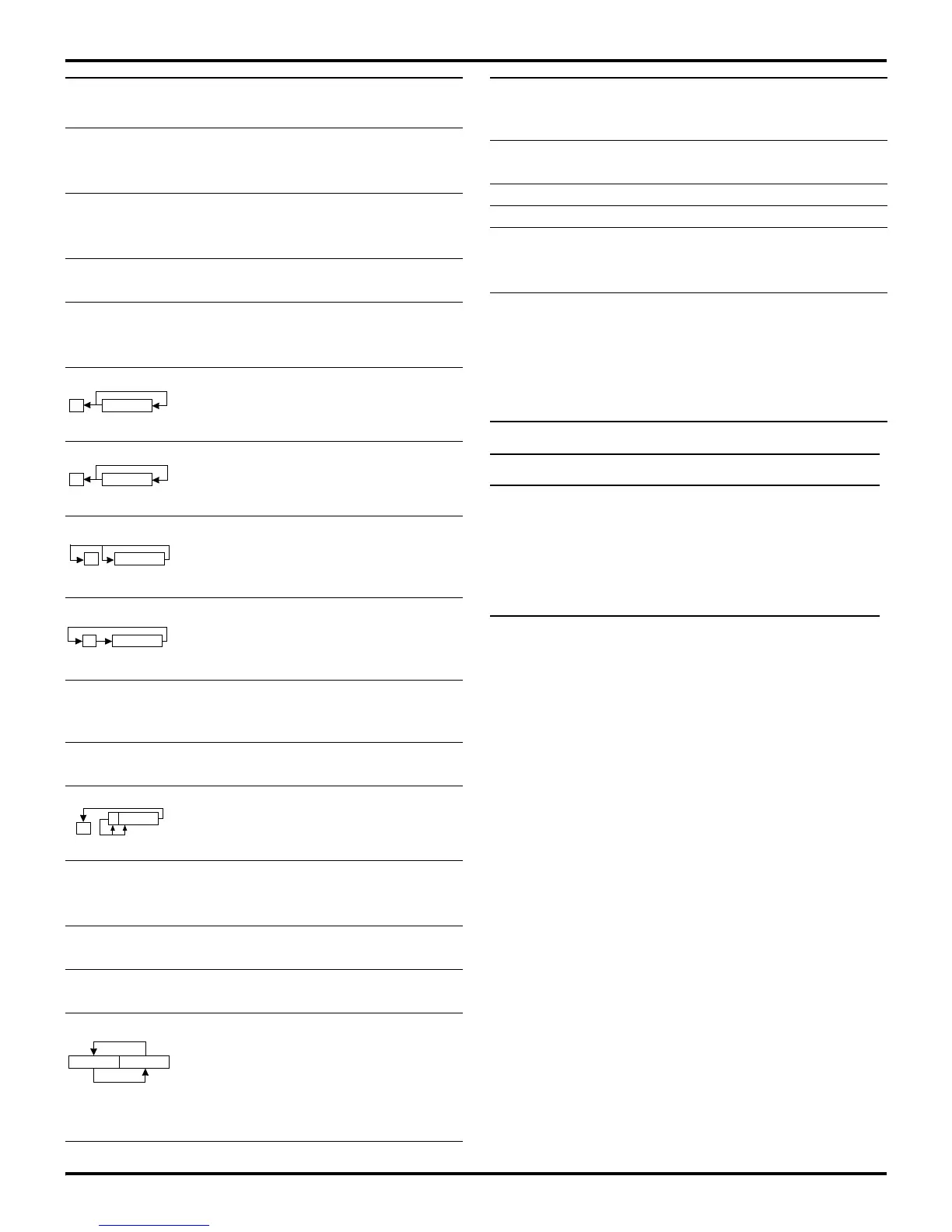

RL dst R

IR

90

91

✻ ✻ ✻ ✻

– –

RLC dst R

IR

10

11

✻ ✻ ✻ ✻

– –

RR dst R

IR

E 0

E 1

✻ ✻ ✻ ✻

– –

RRC dst R C 0

✻ ✻ ✻ ✻

– –

IR C 1

SBC dst, src † 3[ ]

✻ ✻ ✻ ✻

1

✻

dst ← dst – src –

C

SCF D F 1 – – – – –

C ← 1

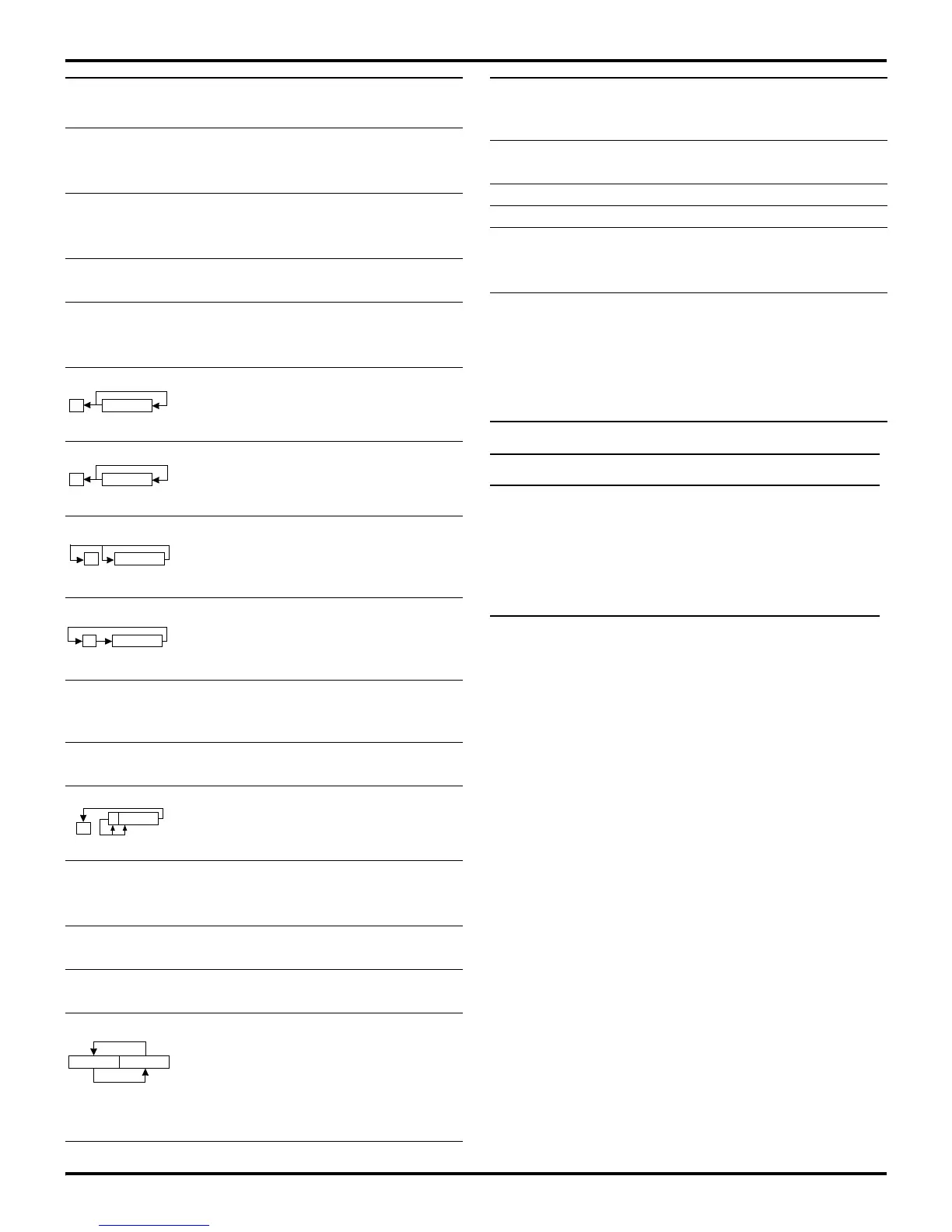

SRA dst R D 0

✻ ✻ ✻

0 – –

IR D 1

SRP dst Im 31 – – – – – –

RP ← src

STOP 6 F – – – – – –

SUB dst, src † 2[ ]

✻ ✻ ✻ ✻

1

✻

dst ← dst – src

SWAP dst R

IR

F0

F1

X

✻ ✻

X – –

Instruction

Address

Mode

Opcode

Byte Flags Affected

and Operation dst src (Hex) C Z S V D H

C

7

0

C

7

0

C

7

0

C

7

0

C

7

0

7

4

3

0

TCM dst, src † 6[ ] –

✻ ✻

0 – –

(NOT dst) AND

src

TM dst, src † 7[ ] –

✻ ✻

0 – –

dst AND src

WDH 4 F – X X X – –

WDT 5 F – X X X – –

XOR dst, src † 7[ ] –

✻ ✻

0 – –

dst AND src

XOR src

Note: † These instructions have an identical set of addressing modes,

which are encoded for brevity. The first opcode nibble is found in the

instruction set table above. The second nibble is expressed symbolically

by a ‘[ ]’ in this table, and its value is found in the following table to

the left of the applicable addressing mode pair. For example, the opcode

of an ADC instruction using the addressing modes r (destination) and Ir

(source) is 13.

Address Mode Lower

dst src Op Code Nibble

r r [2]

r Ir [3]

R R [4]

R IR [5]

R IM [6]

IR IM [7]

Loading...

Loading...